Junction Field Effect Transistors

Ang Junction Field Effect Transistors ay mga transistor na nakabatay sa semiconductor na kinokontrol ng boltahe. Ang mga ito ay unidirectional transistors na may tatlong terminal; drain, source at gate. Ang mga JFET ay walang mga PN junction, ngunit sila ay binubuo ng mga channel ng mga semiconductor na materyales.

Konstruksyon at Pag-uuri

Ang mga JFET ay may malaking channel para sa daloy ng karamihan sa mga carrier ng singil. Ang channel na ito ay kilala bilang substrate. Ang substrate ay maaaring P-type o N-type na materyal. Dalawang panlabas na contact na kilala bilang ohmic contact ang inilalagay sa dalawang dulo ng channel. Ang mga JFET ay inuri batay sa materyal na semiconductor ng substrate sa kanilang pagtatayo.

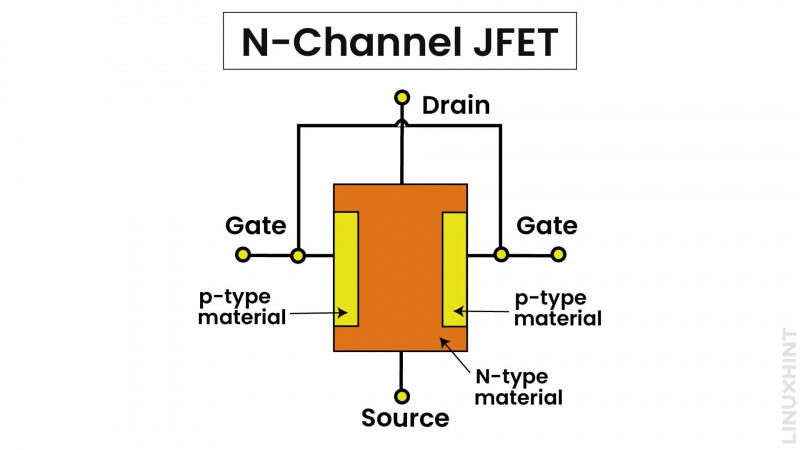

N-Channel JFET Transistors

Ang channel ay ginawa mula sa N-type na impurity material, habang ang mga gate ay binubuo ng P-type na impurity material. Ang N-type na materyal ay nangangahulugan na ang pentavalent impurities ay na-doped, at ang karamihan sa mga carrier ng charge ay mga libreng electron sa channel. Ang pangunahing konstruksyon at simbolikong presentasyon ng mga N-Channel JFET ay ipinapakita sa ibaba:

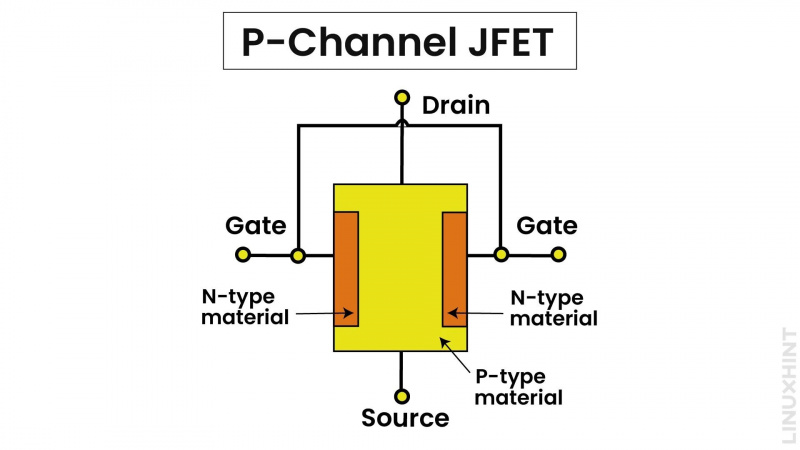

P-Channel JFET Transistors

Ang channel ay binubuo ng P-type na impurity material habang ang mga gate ay binubuo ng N-type na impurity material. Nangangahulugan ang P-Channel na ang mga trivalent impurities ay na-doped sa channel at ang karamihan sa mga carrier ng charge ay mga butas. Ang pangunahing konstruksyon at simbolikong presentasyon ng P-Channel JFET ay ipinapakita sa ibaba:

Paggawa ng mga JFET

Ang mga JFET ay madalas na inilarawan sa pagkakatulad ng pipe ng hose ng tubig. Ang daloy ng tubig sa pamamagitan ng mga tubo ay kahalintulad sa daloy ng mga electron sa pamamagitan ng mga channel ng JFET. Ang pagpiga ng tubo ng tubig ay nagpapasya sa dami ng daloy ng tubig. Katulad nito, sa kaso ng mga JFET, ang paglalapat ng mga boltahe sa mga terminal ng gate ay nagpapasya sa pagpapaliit o pagpapalawak ng channel para sa paggalaw ng mga singil mula sa pinagmulan patungo sa alisan ng tubig.

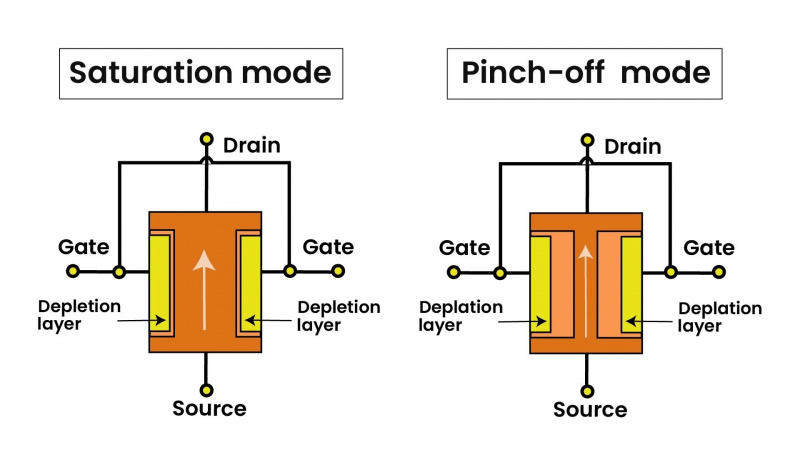

Kapag inilapat ang reverse bias na boltahe sa gate at source, lumiliit ang channel habang tumataas ang depletion layer. Ang mode ng operasyon na ito ay tinatawag na pinch-off mode. Ang ganitong uri ng pag-uugali ng channel ay kinakatawan sa ibaba:

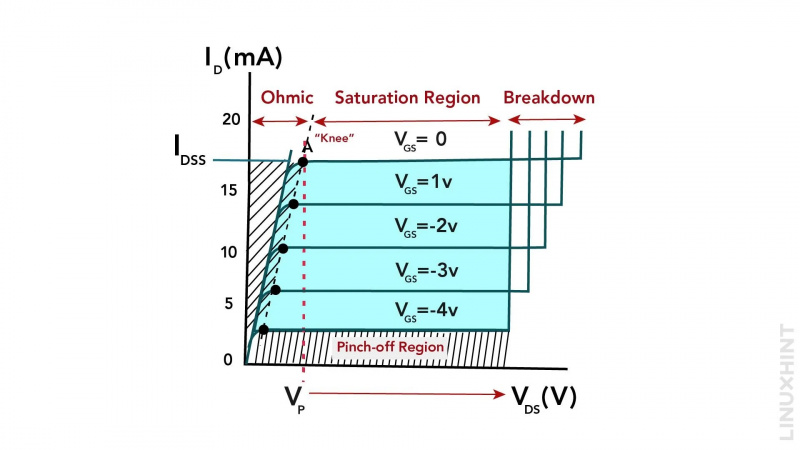

Curve ng Mga Katangian ng JFET

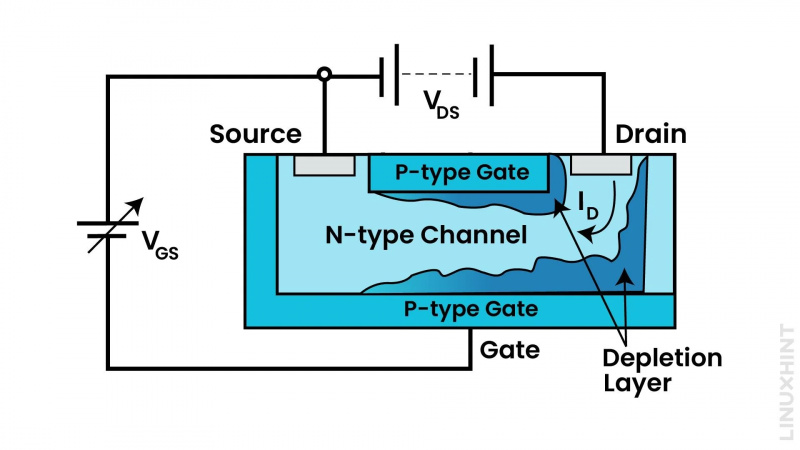

Ang mga JFET ay mga depletion mode device, na nangangahulugang gumagana ang mga ito sa pagpapalawak o pagpapaliit ng mga layer ng depletion. Upang suriin ang kumpletong mga mode ng operasyon, ang sumusunod na pag-aayos ng biasing ay inilalapat sa isang N-Channel JFET.

Dalawang magkaibang biasing na boltahe ang inilalapat sa mga terminal ng JFET. Ang VDS ay inilalapat sa pagitan ng drain at source habang ang VGS ay inilalapat sa pagitan ng gate at source gaya ng ipinapakita sa figure sa itaas.

Ang JFET ay dapat gumana sa apat na magkakaibang paraan ng pagpapatakbo, gaya ng tinalakay sa ibaba.

1: Ohmic Mode

Ang Ohmic mode ay isang normal na estado na walang anumang biasing na boltahe na inilalapat sa mga terminal nito. Samakatuwid, VGS=0 sa ohmic mode. Ang depletion layer ay dapat na napakanipis at ang JFET ay gumagana tulad ng isang ohmic na elemento tulad ng isang risistor.

2: Pinch-Off Mode

Sa cut-off mode, inilapat ang sapat na biasing boltahe sa gate at source. Ang inilapat na reverse bias na boltahe ay umaabot sa depletion na rehiyon sa pinakamataas na antas at samakatuwid ang channel ay kumikilos tulad ng isang bukas na switch na lumalaban sa daloy ng kasalukuyang.

3: Mode ng Saturation

Kinokontrol ng gate at source bias voltage ang kasalukuyang daloy sa channel ng JFET. Ang kasalukuyang ay nag-iiba sa pagbabago sa biasing boltahe. Ang drain at source bias na boltahe ay may hindi gaanong epekto sa mode na ito.

4: Breakdown Mode

Ang drain at source bias na boltahe ay tumataas sa isang antas na sumisira sa depletion layer sa channel ng mga JFET. Ito ay humahantong sa pinakamataas na daloy ng kasalukuyang sa buong channel.

Mga Ekspresyon sa Matematika para sa Mga Parameter ng JFET

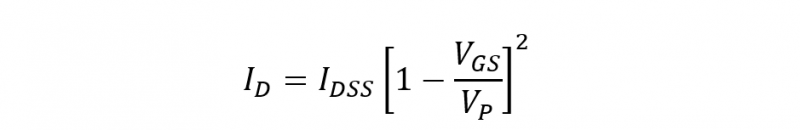

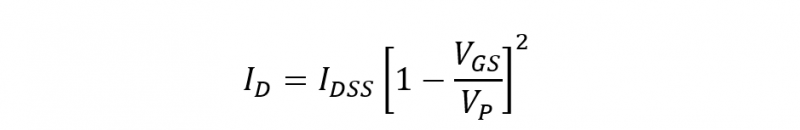

Sa mga mode ng saturation, ang mga JFET ay pumapasok sa mga mode ng konduktor kung saan nag-iiba ang boltahe sa kasalukuyang. Samakatuwid, ang kasalukuyang alisan ng tubig ay maaaring masuri. Ang expression para sa pagsusuri ng drain current ay ibinibigay ng:

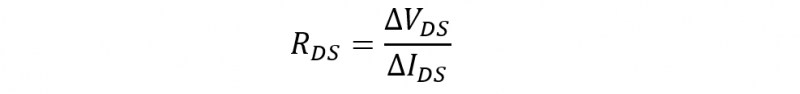

Ang channel ay lumalawak o nagpapaliit sa paggamit ng mga boltahe ng gate. Ang paglaban ng channel na may paggalang sa paggamit ng drain-source boltahe ay ipinahayag bilang:

Ang RDS ay maaari ding kalkulahin sa pamamagitan ng transconductance gain, gm:

Mga Configuration ng JFET

Ang mga JFET ay maaaring konektado sa iba't ibang paraan gamit ang mga boltahe ng input. Ang mga configuration na ito ay kilala bilang common source, common gate at common drain configuration.

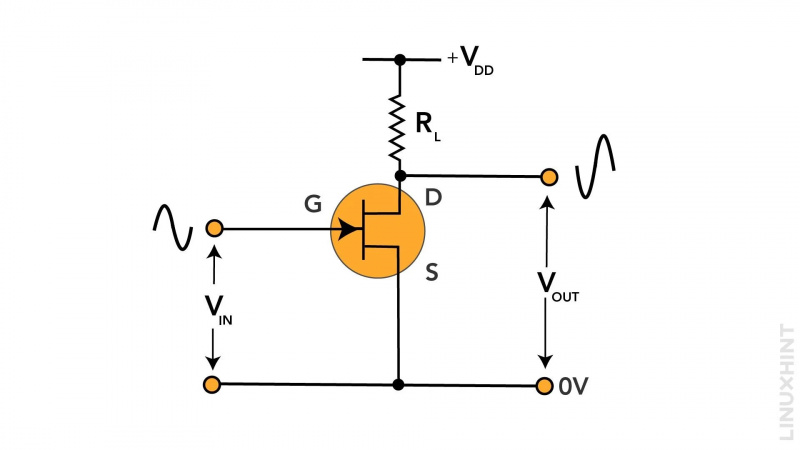

Common Source Configuration

Sa karaniwang source configuration, ang source ng JFET ay grounded at ang input ay konektado sa gate terminal habang ang output ay kinuha mula sa drain. Ang configuration na ito ay nag-aalok ng mataas na input impedance at boltahe amplification function. Ang configuration ng amplifier mode na ito ay ang pinakakaraniwan sa lahat ng configuration ng JFET. Ang output na nakuha ay 180 degrees out of phase na may input.

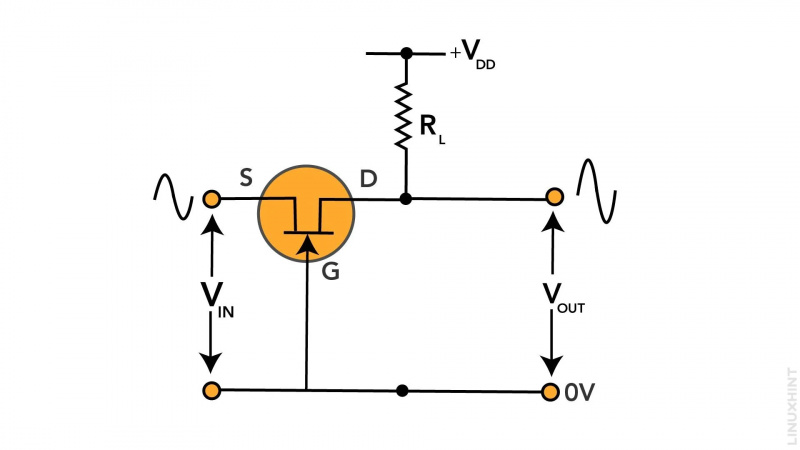

Common Gate Configuration

Sa isang karaniwang configuration ng gate, ang gate ay grounded habang ang input ay konektado sa source at ang output ay kinuha mula sa drain. Dahil ang gate ay konektado sa lupa, ang pagsasaayos ay may mababang input impedance ngunit mas mataas na impedance sa output. Ang output na nakuha ay nasa phase na may input:

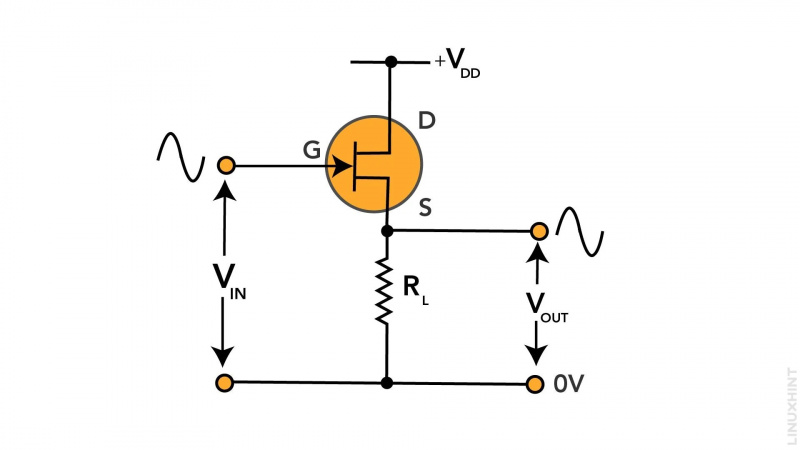

Karaniwang Configuration ng Drain

Sa isang karaniwang drain, ang input ay konektado sa gate habang ang output ay konektado mula sa source terminal. Ang configuration na ito ay nag-aalok din ng mababang input impedance at mas mataas na output impedance tulad ng karaniwang gate configuration, ngunit ang boltahe gain ay humigit-kumulang pagkakaisa dito.

Ang configuration na ito ay tumutugma din sa common source kung saan ang input ay konektado sa gate, ngunit ang common source configuration ay mas mababa sa pagkakaisa.

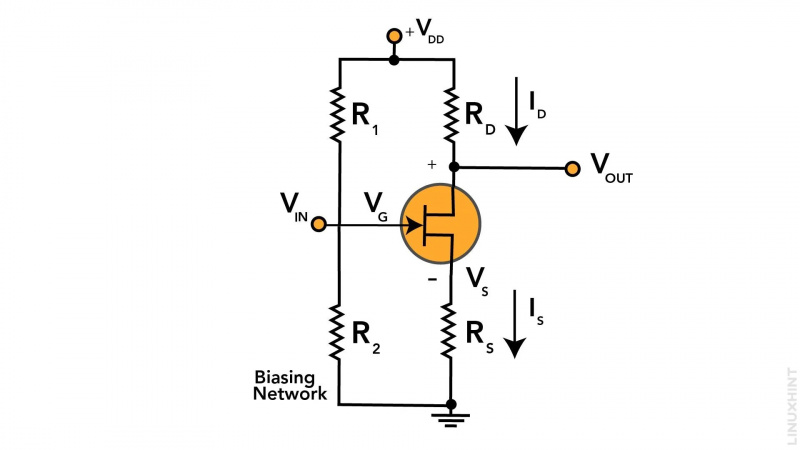

Application – JFETs Amplifier Configuration

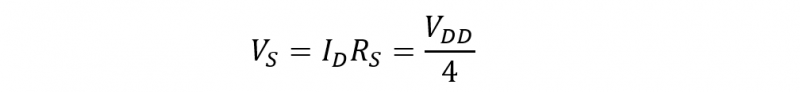

Maaaring gumana ang mga JFET bilang mga amplifier ng Class-A kapag ang terminal ng gate ay konektado sa isang network ng divider ng boltahe. Ang isang panlabas na boltahe ay inilapat sa buong source terminal, na kadalasang naka-configure upang maging isang-kapat ng VDD sa ibabang circuit.

Ang pinagmulan ng boltahe ay maaaring ipahayag bilang:

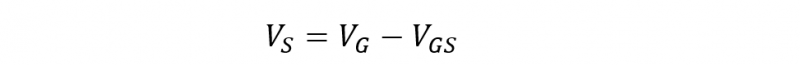

Gayundin, ang boltahe ng pinagmulan ay maaaring kalkulahin sa pamamagitan ng expression sa ibaba:

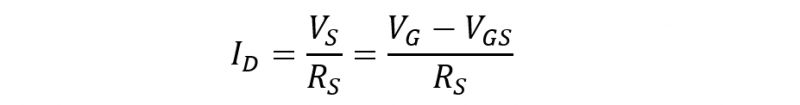

Ang kasalukuyang alisan ng tubig ay maaaring kalkulahin mula sa itaas na pagsasaayos tulad ng nasa ibaba:

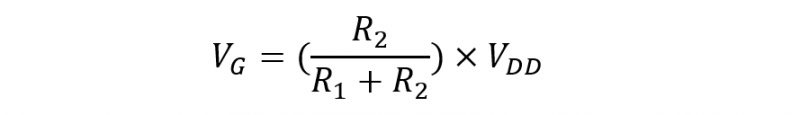

Ang boltahe ng gate ay maaaring makuha bilang isang function ng mga halaga ng resistors R1 & R2 tulad ng ibinigay sa ibaba.

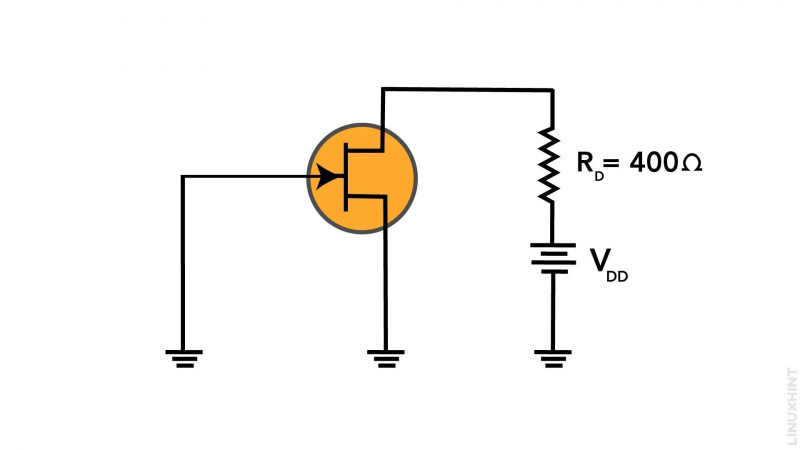

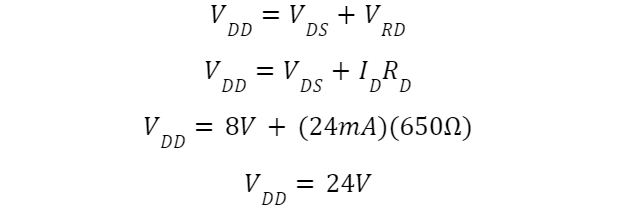

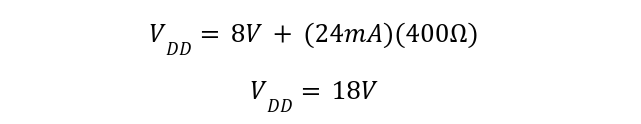

Halimbawa 1: Pagkalkula ng V DD

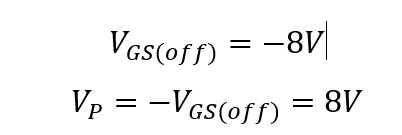

Kung si V GS(off) =-8V, ako DSS =24mA para sa JFET sa ibabang pagsasaayos, kalkulahin ang V DD tulad ng ipinapakita sa figure noong R D =400.

Since

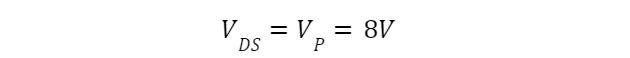

Ang nasa itaas ay ang pinakamababang halaga ng VDS para gumana ang JFET sa patuloy na kasalukuyang rehiyon, samakatuwid:

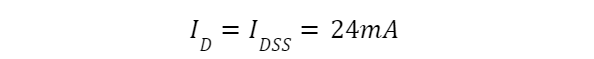

Gayundin,

Sa pamamagitan ng paglalapat ng KVL sa drain circuit:

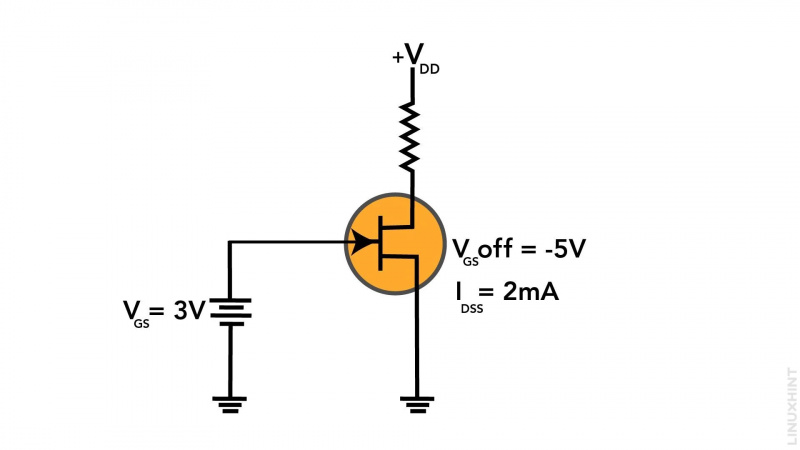

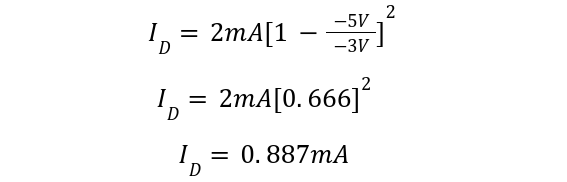

Halimbawa 2: Tukuyin ang Halaga ng Drain Current

Tukuyin ang halaga ng drain current kapag VGS=3V, VGS(Off)=-5V, IDSS=2mA para sa mas mababa sa JFET configuration.

Ang expression para sa drain current ay:

Konklusyon

Ang Junction Field Effect Transistors ay tatlong terminal na semiconductor device na gumagana sa gawi ng mga depletion region sa iba't ibang mode ng operasyon. Wala silang PN junctions, ngunit gawa sila sa mga channel ng mga semiconductor na materyales.