6.1 Panimula

Ang mga modernong computer na pangkalahatang layunin ay may dalawang uri: CISC at RISC. Ang CISC ay kumakatawan sa Complex Instruction Set Computer. Ang RISK ay kumakatawan sa Reduced Instruction Set Computer. Ang 6502 o 6510 microprocessors, kung naaangkop sa Commodore-64 computer, ay higit na katulad ng RISC architecture kaysa sa CISC architecture.

Ang mga RISC computer sa pangkalahatan ay may mas maiikling mga tagubilin sa assembly language (sa bilang ng mga byte) kumpara sa mga CISC computer.

Tandaan : Nakikitungo man sa CISC, RISC, o lumang computer, ang isang peripheral ay nagsisimula mula sa isang panloob na port at lumalabas palabas sa isang panlabas na port sa patayong ibabaw ng unit ng system ng computer (base unit) at sa panlabas na aparato.

Ang isang tipikal na pagtuturo ng isang CISC computer ay makikita tulad ng pagsasama ng ilang maiikling tagubilin sa assembly language sa isang mas mahabang pagtuturo ng assembly language na ginagawang kumplikado ang resultang pagtuturo. Sa partikular, ang isang CISC computer ay naglo-load ng mga operand mula sa memorya patungo sa mga rehistro ng microprocessor, nagsasagawa ng isang operasyon, at pagkatapos ay iniimbak ang resulta pabalik sa memorya, lahat sa isang pagtuturo. Sa kabilang banda, ito ay hindi bababa sa tatlong mga tagubilin (maikli) para sa RISC computer.

Mayroong dalawang sikat na serye ng mga CISC computer: ang Intel microprocessor computer at ang AMD microprocessor computer. Ang AMD ay nangangahulugang Advanced Micro Devices; ito ay isang semiconductor manufacturing company. Ang serye ng intel microprocessor, sa pagkakasunud-sunod ng pagbuo, ay 8086, 8088, 80186, 80286, 80386, 80486, Pentium, Core, i Series, Celeron, at Xeon. Ang mga tagubilin sa wika ng pagpupulong para sa mga unang microprocessor ng intel tulad ng 8086 at 8088 ay hindi masyadong kumplikado. Gayunpaman, ang mga ito ay kumplikado para sa mga bagong microprocessor. Ang kamakailang AMD microprocessors para sa CISC series ay Ryzen, Opteron, Athlon, Turion, Phenom, at Sempron. Ang Intel at AMD microprocessors ay kilala bilang x86 microprocessors.

Ang ARM ay nangangahulugang Advanced RISC Machine. Ang mga arkitektura ng ARM ay tumutukoy sa isang pamilya ng mga processor ng RISC na angkop para sa paggamit sa iba't ibang uri ng mga application. Bagama't maraming Intel at AMD microprocessors ang ginagamit sa desktop Personal Computers, maraming ARM processor ang nagsisilbing embedded processor sa mga safety-critical system gaya ng automotive anti-lock brakes at bilang general-purpose processor sa mga smartwatch, portable phone, tablet, at laptop computer. . Bagama't ang parehong uri ng microprocessor ay makikita sa maliliit at malalaking device, ang RISC microprocessors ay mas makikita sa maliliit na device kaysa sa malalaking device.

Computer Word

Kung ang isang computer ay sinasabing isang computer na may 32 bits na salita, nangangahulugan ito na ang impormasyon ay iniimbak, inililipat, at minamanipula sa anyo ng tatlumpu't dalawang-bit na binary code sa loob ng panloob na bahagi ng motherboard. Nangangahulugan din ito na ang pangkalahatang layunin na mga rehistro sa microprocessor ng computer ay 32-bits ang lapad. Ang A, X, at Y na mga rehistro ng 6502 microprocessor ay mga pangkalahatang layunin na rehistro. Ang mga ito ay walong-bit ang lapad, at kaya ang Commodore-64 na computer ay isang walong-bit na word computer.

Ilang Bokabularyo

X86 na mga Computer

Ang mga kahulugan ng byte, salita, doubleword, quadword, at double-quadword ay ang mga sumusunod para sa x86 na mga computer:

- Byte : 8 bits

- salita : 16 bits

- Dobleng salita : 32 bits

- Quadword : 64 bits

- Dobleng quadword : 128 bits

Mga ARM na Computer

Ang mga kahulugan ng byte, halfword, word, at doubleword ay ang mga sumusunod para sa mga ARM na computer:

- Byte : 8 bits

- Maging kalahati : 16 bits

- salita : 32 bits

- Dobleng salita : 64 bits

Dapat tandaan ang mga pagkakaiba at pagkakatulad para sa x86 at ARM na mga pangalan (at mga halaga).

Tandaan : Ang mga sign integer sa parehong uri ng computer ay complement ng dalawa.

Lokasyon ng Memorya

Sa Commodore-64 computer, ang isang lokasyon ng memorya ay karaniwang isang byte ngunit maaaring dalawang magkasunod na byte paminsan-minsan kapag isinasaalang-alang ang mga pointer (indirect addressing). Sa modernong x86 computer, ang lokasyon ng memorya ay 16 na magkakasunod na byte kapag nakikitungo sa dobleng quadword na 16 byte (128 bits), 8 magkakasunod na byte kapag nakikipag-usap sa quadword na 8 bytes (64 bits), 4 na magkakasunod na byte kapag nakikitungo sa doubleword ng 4 byte (32 bits), 2 magkakasunod na byte kapag nakikipag-usap sa isang salita na 2 byte (16 bits), at 1 byte kapag nakikipag-usap sa isang byte (8 bits). Sa modernong ARM computer, ang lokasyon ng memorya ay 8 magkakasunod na byte kapag nakikitungo sa isang doubleword na 8 bytes (64 bits), 4 na magkakasunod na byte kapag nakikipag-usap sa isang salita na 4 bytes (32 bits), 2 magkakasunod na byte kapag nakikitungo sa isang halfword ng 2 byte (16 bits), at 1 byte kapag nakikitungo sa isang byte (8 bits).

Ipinapaliwanag ng kabanatang ito kung ano ang karaniwan sa mga arkitektura ng CISC at RISC at kung ano ang kanilang mga pagkakaiba. Ginagawa ito kumpara sa 6502 µP at sa commodore-64 computer kung saan ito naaangkop.

6.2 Motherboard Block Diagram ng Modern PC

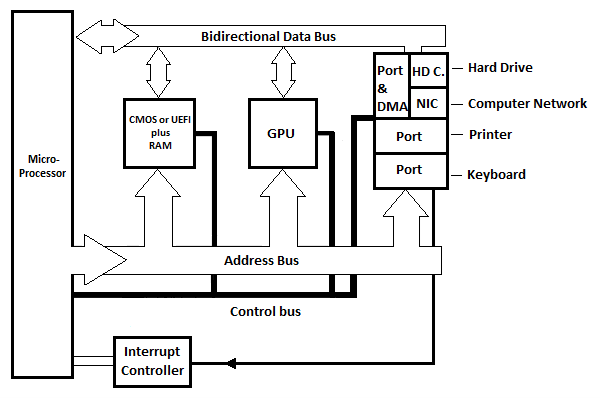

Ang ibig sabihin ng PC ay Personal Computer. Ang sumusunod ay isang generic na pangunahing block diagram para sa isang modernong motherboard na may isang microprocessor para sa isang personal na computer. Ito ay kumakatawan sa isang CISC o RISC motherboard.

Fig. 6.21 Pangunahing Motherboard Block Diagram ng Modern PC

Tatlong panloob na port ang ipinapakita sa diagram, ngunit may higit pa sa pagsasanay. Ang bawat port ay may rehistro na makikita bilang ang port mismo. Ang bawat port circuit ay may hindi bababa sa isa pang rehistro na maaaring tawaging 'status register'. Ang status register ay nagpapahiwatig ng port sa program na nagpapadala ng interrupt signal sa microprocessor. Mayroong interrupt controller circuit (hindi ipinakita) na nag-iiba sa pagitan ng iba't ibang interrupt na linya mula sa iba't ibang port at may ilang linya lang papunta sa µP.

Ang HD.C sa diagram ay kumakatawan sa Hard Drive Card. Ang NIC ay kumakatawan sa Network Interface Card. Ang hard drive card (circuit) ay konektado sa hard drive na nasa loob ng base unit (system unit) ng modernong computer. Ang network interface card (circuit) ay konektado sa pamamagitan ng isang panlabas na cable sa isa pang computer. Sa diagram, mayroong isang port at isang DMA (sumangguni sa sumusunod na paglalarawan) na konektado sa hard disk card at/o sa network interface card. Ang DMA ay kumakatawan sa Direct Memory Access.

Tandaan mula sa Commodore-64 computer chapter na upang maipadala ang mga byte mula sa memory sa disk drive o ibang computer, ang bawat byte ay kailangang kopyahin sa isang rehistro sa microprocessor bago makopya sa kaukulang panloob na port, at pagkatapos ay awtomatikong sa device. Upang matanggap ang mga byte mula sa disk drive o isa pang computer sa memorya, ang bawat byte ay kailangang kopyahin mula sa kaukulang internal port register sa isang microprocessor register bago makopya sa memorya. Karaniwan itong tumatagal kung ang bilang ng mga byte sa stream ay malaki. Ang solusyon para sa mabilis na paglipat ay ang paggamit ng Direct Memory Access (circuit) nang hindi dumadaan sa microprocessor.

Ang DMA circuit ay nasa pagitan ng port at ng HD. C o NIC. Sa direktang pag-access sa memorya ng DMA circuit, ang paglipat ng malalaking stream ng bytes ay direkta sa pagitan ng DMA circuit at ng memorya (RAM) nang walang patuloy na paglahok ng microprocessor. Ginagamit ng DMA ang address bus at ang data bus bilang kapalit ng µP. Ang kabuuang tagal ng paglipat ay mas maikli kaysa sa kung ang µP hard ang gagamitin. Parehong ginagamit ng HD C. o NIC ang DMA kapag mayroon silang malaking stream ng data (bytes) para sa paglipat gamit ang RAM (ang memorya).

Ang GPU ay kumakatawan sa Graphics Processing Unit. Ang bloke na ito sa motherboard ay may pananagutan sa pagpapadala ng teksto at ang gumagalaw o hindi gumagalaw na mga imahe sa screen.

Sa modernong mga computer (PC), walang Read Only Memory (ROM). Gayunpaman, mayroong BIOS o UEFI na isang uri ng non-volatile RAM. Ang impormasyon sa BIOS ay aktwal na pinananatili ng isang baterya. Ang baterya ang talagang nagpapanatili ng timer ng orasan pati na rin, sa tamang oras at petsa para sa computer. Ang UEFI ay naimbento pagkatapos ng BIOS, at pinalitan ang BIOS kahit na ang BIOS ay may kaugnayan pa rin sa mga modernong PC. Tatalakayin pa natin ang mga ito mamaya!

Sa modernong mga PC, ang address at data bus sa pagitan ng µP at ng mga internal port circuit (at memory) ay hindi parallel bus. Ang mga ito ay mga serial bus na nangangailangan ng dalawang konduktor para sa paghahatid sa isang direksyon at isa pang dalawang konduktor para sa paghahatid sa kabilang direksyon. Nangangahulugan ito, halimbawa, na ang 32-bit ay maaaring ipadala sa serye (isang bit pagkatapos ng isa) sa alinmang direksyon.

Kung ang serial transmission ay nasa isang direksyon lamang na may dalawang conductor (dalawang linya), iyon ay sinasabing half-duplex. Kung ang serial transmission ay nasa parehong direksyon na may apat na konduktor, isang pares sa alinmang direksyon, iyon ay sinasabing full-duplex.

Ang buong memorya ng modernong computer ay binubuo pa rin ng isang serye ng mga byte na lokasyon: walong-bit bawat byte. Ang isang modernong computer ay may memory space na hindi bababa sa 4 giga bytes = 4 x 210 x 2 10 x 2 10 = 4 x 1,073,741,824 10 byte = 4 x 1024 10/sub> x 1024 10 x 1024 10 = 4 x 1,073,741,824 10 .

Tandaan : Kahit na walang timer circuit na ipinapakita sa nakaraang motherboard, lahat ng modernong motherboard ay may timer circuit.

6.3 Ang x64 Computer Architecture Basics

6.31 Ang x64 Register Set

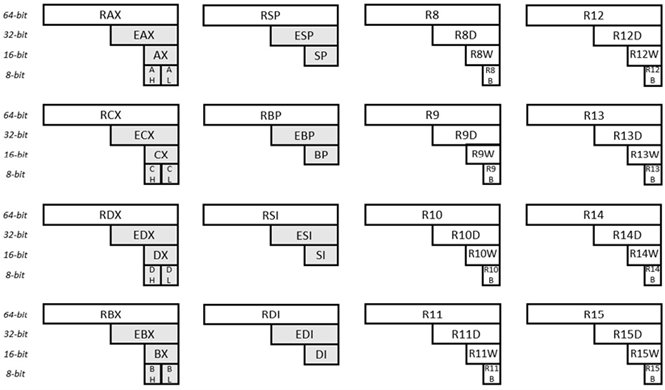

Ang 64-bit microprocessor ng x86 series ng microprocessors ay isang 64-bit microprocessor. Ito ay medyo moderno upang palitan ang 32-bit na processor ng parehong serye. Ang pangkalahatang layunin ng 64-bit microprocessor ay nagrerehistro at ang kanilang mga pangalan ay ang mga sumusunod:

Fig. 6.31 Mga Rehistro ng Pangkalahatang Layunin para sa x64

Labing-anim (16) na rehistro ng pangkalahatang layunin ang ipinapakita sa ibinigay na paglalarawan. Ang bawat isa sa mga rehistrong ito ay 64-bit ang lapad. Sa pagtingin sa rehistro sa itaas na kaliwang sulok, ang 64 bits ay kinilala bilang RAX. Ang unang 32 bits ng parehong register na ito (mula sa kanan) ay kinilala bilang EAX. Ang unang 16 bits ng parehong rehistro (mula sa kanan) ay kinilala bilang AX. Ang pangalawang byte (mula sa kanan) ng parehong rehistro ay kinilala bilang AH (H dito ay nangangahulugang mataas). At ang unang byte (ng parehong rehistro na ito) ay kinilala bilang AL (L dito ay nangangahulugang mababa). Sa pagtingin sa rehistro sa kanang sulok sa ibaba, ang 64 bits ay kinilala bilang R15. Ang unang 32 bits ng parehong rehistro ay kinilala bilang R15D. Ang unang 16 bits ng parehong rehistro ay kinilala bilang R15W. At ang unang byte ay kinilala bilang R15B. Ang mga pangalan ng iba pang mga rehistro (at mga sub na rehistro) ay katulad na ipinaliwanag.

Mayroong ilang mga pagkakaiba sa pagitan ng Intel at ng AMD µPs. Ang impormasyon sa seksyong ito ay para sa Intel.

Sa 6502 µP, ang Program Counter register (hindi direktang naa-access) na nagtataglay ng susunod na pagtuturo na isasagawa ay 16-bits ang lapad. Dito (x64), ang program counter ay tinatawag na Instruction Pointer, at ito ay 64-bits ang lapad. Ito ay may label na RIP. Nangangahulugan ito na ang x64 µP ay maaaring tumugon ng hanggang 264 = 1.844674407 x 1019 (talagang 18,446,744,073,709,551,616) na lokasyon ng memory byte. Ang RIP ay hindi isang pangkalahatang layunin na rehistro.

Ang Stack Pointer Register o RSP ay kabilang sa 16 na pangkalahatang layunin na rehistro. Tumuturo ito sa huling stack entry sa memorya. Tulad ng 6502 µP, ang stack para sa x64 ay lumalaki pababa. Gamit ang x64, ang stack sa RAM ay ginagamit upang iimbak ang mga return address para sa mga subroutine. Ginagamit din ito para sa pag-iimbak ng “shadow space” (sumangguni sa sumusunod na talakayan).

Ang 6502 µP ay may 8-bit na processor status register. Ang katumbas sa x64 ay tinatawag na rehistro ng RFLAGS. Ang rehistrong ito ay nag-iimbak ng mga flag na ginagamit para sa mga resulta ng mga operasyon at para sa pagkontrol sa processor (µP). Ito ay 64-bits ang lapad. Ang mas mataas na 32 bits ay nakalaan at hindi kasalukuyang ginagamit. Ang sumusunod na talahanayan ay nagbibigay ng mga pangalan, index, at mga kahulugan para sa karaniwang ginagamit na mga piraso sa rehistro ng RFLAGS:

| Talahanayan 6.31.1 Pinaka ginagamit na mga Flag ng RFLAGS (Bits) |

|||

|---|---|---|---|

| Simbolo | bit | Pangalan | Layunin |

| CF | 0 | dalhin | Ito ay itinakda kung ang isang aritmetika na operasyon ay bumubuo ng isang carry o isang paghiram mula sa pinaka makabuluhang bit ng resulta; na-clear kung hindi man. Ang flag na ito ay nagpapahiwatig ng overflow na kundisyon para sa unsigned-integer arithmetic. Ginagamit din ito sa multiple-precision na arithmetic. |

| PF | 2 | Pagkakapantay-pantay | Ito ay itinakda kung ang hindi gaanong makabuluhang byte ng resulta ay naglalaman ng pantay na bilang ng 1 bits; na-clear kung hindi man. |

| NG | 4 | Ayusin | Ito ay nakatakda kung ang isang arithmetic operation ay bumubuo ng isang carry o isang paghiram sa bit 3 ng resulta; na-clear kung hindi man. Ginagamit ang flag na ito sa binary-coded decimal (BCD) arithmetic. |

| ZF | 6 | Zero | Ito ay nakatakda kung ang resulta ay zero; na-clear kung hindi man. |

| SF | 7 | Tanda | Ito ay nakatakda kung ito ay katumbas ng pinaka-makabuluhang bit ng resulta na kung saan ay ang sign bit ng isang sign integer (0 ay nagpapahiwatig ng isang positibong halaga at 1 ay nagpapahiwatig ng isang negatibong halaga). |

| NG | labing-isa | Pag-apaw | Ito ay itinakda kung ang resulta ng integer ay masyadong malaki isang positibong numero o masyadong maliit na negatibong numero (hindi kasama ang sign-bit) upang magkasya sa patutunguhang operand; na-clear kung hindi man. Ang flag na ito ay nagpapahiwatig ng overflow na kundisyon para sa signed-integer (two's complement) arithmetic. |

| DF | 10 | Direksyon | Ito ay nakatakda kung ang mga tagubilin sa string ng direksyon ay gumagana (pagtaas o pagbaba). |

| ID | dalawampu't isa | Pagkakakilanlan | Ito ay nakatakda kung ang pagbabago nito ay nagpapahiwatig ng pagkakaroon ng pagtuturo ng CPUID. |

Bilang karagdagan sa labingwalong 64-bit na rehistro na dating ipinahiwatig, ang x64 architecture µP ay may walong 80-bit na malawak na rehistro para sa floating point aritmetika. Ang walong register na ito ay maaari ding gamitin bilang mga MMX register (sumangguni sa sumusunod na talakayan). Mayroon ding labing-anim na 128-bit na rehistro para sa XMM (sumangguni sa sumusunod na talakayan).

Iyan ay hindi lahat tungkol sa mga rehistro. Mayroong higit pang mga rehistro ng x64 na mga rehistro ng segment (karamihan ay hindi ginagamit sa x64), mga rehistro ng kontrol, mga rehistro ng pamamahala ng memorya, mga rehistro ng debug, mga rehistro ng virtualization, mga rehistro ng pagganap na sumusubaybay sa lahat ng uri ng mga panloob na parameter (mga hit/namimiss ng cache, mga micro-op na naisakatuparan, timing , at marami pang iba).

SIMD

SIMD ay kumakatawan sa Single Instruction Multiple Data. Nangangahulugan ito na ang isang pagtuturo ng wika ng pagpupulong ay maaaring kumilos sa maraming data nang sabay sa isang microprocessor. Isaalang-alang ang sumusunod na talahanayan:

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | |

| + | 9 | 10 | labing-isa | 12 | 13 | 14 | labinlima | 16 |

| = | 10 | 12 | 14 | 16 | 18 | dalawampu | 22 | 24 |

Sa talahanayang ito, walong pares ng mga numero ang idinaragdag nang magkatulad (sa parehong tagal) upang magbigay ng walong sagot. Maaaring gawin ng isang pagtuturo ng assembly language ang walong parallel integer na pagdaragdag sa mga MMX register. Ang isang katulad na bagay ay maaaring gawin sa mga rehistro ng XMM. Kaya, mayroong mga tagubilin sa MMX para sa mga integer at mga tagubilin sa XMM para sa mga float.

6.32 Memory Map at ang x64

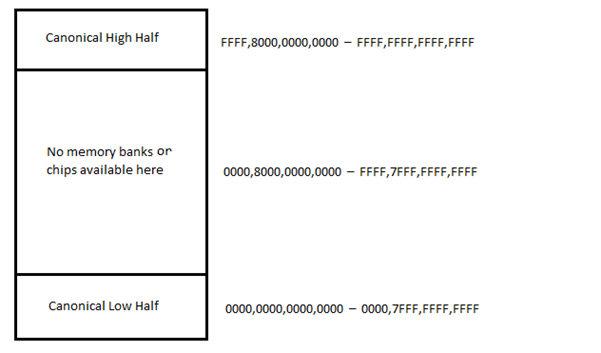

Gamit ang Instruction Pointer (Program Counter) na mayroong 64 bits, nangangahulugan ito na ang 264 = 1.844674407 x 1019 na mga lokasyon ng memory byte ay maaaring matugunan. Sa hexadecimal, ang pinakamataas na byte na lokasyon ay FFFF,FFFF,FFFF,FFFF16. Walang ordinaryong computer ngayon ang makakapagbigay ng ganoong kalaking memorya (kumpleto) na espasyo. Kaya, ang isang angkop na mapa ng memorya para sa x64 computer ay ang mga sumusunod:

Pansinin na ang gap mula 0000,8000,0000,000016 hanggang FFFF,7FFF,FFFF,FFFF16 ay walang mga lokasyon ng memorya (walang memory RAM banks). Ito ay isang pagkakaiba ng FFFF,0000,0000,000116 na medyo malaki. Ang canonical high half ay may operating system, habang ang canonical low half ay may mga user program (application) at data. Ang operating system ay binubuo ng dalawang bahagi: isang maliit na UEFI (BIOS) at isang malaking bahagi na na-load mula sa hard drive. Ang susunod na kabanata ay nagsasalita nang higit pa tungkol sa mga modernong operating system. Pansinin ang pagkakatulad sa memory map na ito at para sa Commodore-64 kapag ang 64KB ay maaaring mukhang maraming memorya.

Sa kontekstong ito, ang operating system ay halos tinatawag na 'kernel'. Ang kernel ay katulad ng Kernal ng Commodore-64 computer, ngunit may higit pang mga subroutine.

Ang endianness para sa x64 ay maliit na endian, na nangangahulugang para sa isang lokasyon, ang mas mababang address ay tumuturo sa mas mababang byte ng nilalaman sa memorya.

6.33 Assembly Language Addressing Modes para sa x64

Ang mga mode ng pagtugon ay ang mga paraan kung saan maaaring ma-access ng isang pagtuturo ang mga rehistro ng µP at ang memorya (kabilang ang mga rehistro ng panloob na port). Ang x64 ay maraming addressing mode, ngunit ang karaniwang ginagamit na addressing mode lang ang tinutugunan dito. Ang pangkalahatang syntax para sa isang pagtuturo dito ay:

opcode destinasyon, source

Ang mga decimal na numero ay isinusulat nang walang anumang prefix o suffix. Gamit ang 6502, ang pinagmulan ay implicit. Ang x64 ay may mas maraming op-code kaysa sa 6502, ngunit ang ilan sa mga opcode ay may parehong mnemonics. Ang mga indibidwal na tagubilin sa x64 ay may variable na haba at maaaring may sukat mula 1 hanggang 15 byte. Ang karaniwang ginagamit na mga mode ng pagtugon ay ang mga sumusunod:

Mode ng Agarang Pag-address

Dito, ang source operand ay isang aktwal na halaga at hindi isang address o label. Halimbawa (basahin ang komento):

ADD EAX, 14 ; magdagdag ng decimal 14 hanggang 32-bit EAX ng 64-bit RAX, ang sagot ay mananatili sa EAX (destinasyon)

Magrehistro sa Register Addressing Mode

Halimbawa:

ADD R8B, AL ; magdagdag ng 8-bit AL ng RAX sa R8B ng 64-bit R8 - ang mga sagot ay nananatili sa R8B (destinasyon)

Hindi Direkta at Indexed Addressing Mode

Ang hindi direktang pagtugon sa 6502 µP ay nangangahulugan na ang lokasyon ng ibinigay na address sa pagtuturo ay may epektibong address (pointer) ng huling lokasyon. Ang isang katulad na bagay ay nangyayari sa x64. Ang index addressing gamit ang 6502 µP ay nangangahulugan na ang nilalaman ng isang µP register ay idinaragdag sa ibinigay na address sa pagtuturo upang magkaroon ng epektibong address. Ang isang katulad na bagay ay nangyayari sa x64. Gayundin, sa x64, ang nilalaman ng rehistro ay maaari ding i-multiply sa 1 o 2 o 4 o 8 bago idagdag sa ibinigay na address. Ang pagtuturo ng mov (kopya) ng x64 ay maaaring pagsamahin ang parehong hindi direkta at naka-index na pag-address. Halimbawa:

MOV R8W, 1234[8*RAX+RCX] ; ilipat ang salita sa address (8 x RAX + RCX) + 1234

Dito, ang R8W ay may unang 16-bit ng R8. Ang ibinigay na address ay 1234. Ang rehistro ng RAX ay may 64-bit na numero na pinarami ng 8. Ang resulta ay idinagdag sa nilalaman ng 64-bit na RCX na rehistro. Ang pangalawang resulta ay idinagdag sa ibinigay na address na 1234 upang makuha ang epektibong address. Ang numero sa lokasyon ng epektibong address ay inilipat (kopyahin) sa unang 16-bit na lugar (R8W) ng rehistro ng R8, na pinapalitan ang anumang naroroon. Pansinin ang paggamit ng mga square bracket. Tandaan na ang isang salita sa x64 ay 16-bits ang lapad.

RIP Relative Addressing

Para sa 6502 µP, ang relative addressing ay ginagamit lamang sa mga tagubilin ng sangay. Doon, ang solong operand ng opcode ay isang offset na idinaragdag o ibinabawas sa nilalaman ng Program Counter para sa epektibong address ng pagtuturo (hindi address ng data). Ang isang katulad na bagay ay nangyayari sa x64 kung saan ang Program Counter ay tinatawag bilang Instruction Pointer. Ang pagtuturo na may x64 ay hindi lamang kailangang isang pagtuturo ng sangay. Ang isang halimbawa ng RIP-relative addressing ay:

MOV AL, [RIP]

Ang AL ng RAX ay may 8-bit signed number na idinaragdag o ibinabawas mula sa nilalaman sa RIP (64-bit instruction pointer) upang tumuro sa susunod na pagtuturo. Tandaan na ang pinagmulan at patutunguhan ay kakaibang pinagpalit sa pagtuturong ito. Tandaan din ang paggamit ng mga square bracket na tumutukoy sa nilalaman ng RIP.

6.34 Mga Karaniwang Ginagamit na Tagubilin ng x64

Sa sumusunod na talahanayan * ay nangangahulugang iba't ibang posibleng mga suffix ng isang subset ng mga opcode:

| Talahanayan 6.34.1 Mga Karaniwang Ginagamit na Tagubilin sa x64 |

|

|---|---|

| Opcode | Ibig sabihin |

| MOV | Ilipat (kopya) papunta/mula/sa pagitan ng memorya at mga rehistro |

| CMOV* | Iba't ibang conditional moves |

| XCHG | Palitan |

| BSWAP | Pagpalit ng byte |

| PUSH/POP | Paggamit ng stack |

| ADD/ADC | Magdagdag/may dala |

| SUB/SBC | Ibawas/may dala |

| MUL/IMUL | Multiply/unsigned |

| DIV/IDIV | Divide/unsigned |

| INC/DEC | Pagtaas/Pagbawas |

| NEG | Negate |

| CMP | Ikumpara |

| AT/O/XOR/HINDI | Mga pagpapatakbo ng bitwise |

| SHR/SAR | Ilipat pakanan ang lohikal/aritmetika |

| SHL/SAL | Lumipat pakaliwa sa lohikal/aritmetika |

| ROR/ROLE | I-rotate pakanan/kaliwa |

| RCR/RCL | I-rotate pakanan/kaliwa sa pamamagitan ng carry bit |

| BT/BTS/BTR | Bit test/at itakda/at i-reset |

| JMP | Unconditional jump |

| JE/JNE/JC/JNC/J* | Tumalon kung pantay/hindi pantay/ dala/hindi dala/marami pang iba |

| LAKAD/LALAKAD/LALAKAD | I-loop gamit ang ECX |

| TUMAWAG/RET | Tumawag sa subroutine/pagbabalik |

| HINDI | Walang operasyon |

| CPUID | impormasyon ng CPU |

Ang x64 ay may mga tagubilin para sa multiply at divide. Mayroon itong multiplication at division hardware circuits sa µP nito. Ang 6502 µP ay walang multiplication at division hardware circuits. Mas mabilis na gawin ang multiplikasyon at paghahati sa pamamagitan ng hardware kaysa sa software (kabilang ang paglilipat ng mga bit).

Mga Tagubilin sa String

Mayroong ilang mga tagubilin sa string, ngunit ang isa lamang na tatalakayin dito ay ang pagtuturo ng MOVS (para sa paglipat ng string) upang kopyahin ang isang string na nagsisimula sa address na C000 H . Upang magsimula sa address C100 H , gamitin ang sumusunod na tagubilin:

MOVS [C100H], [C000H]

Pansinin ang suffix H para sa hexadecimal.

6.35 Looping sa x64

Ang 6502 µP ay may mga tagubilin sa sangay para sa pag-loop. Ang isang pagtuturo ng sangay ay tumalon sa isang lokasyon ng address na mayroong bagong pagtuturo. Ang lokasyon ng address ay maaaring tawaging 'loop'. Ang x64 ay mayroong LOOP/LOOPE/LOOPNE na mga tagubilin para sa pag-loop. Ang mga nakareserbang salita sa wikang pagpupulong na ito ay hindi dapat ipagkamali sa label na 'loop' (nang walang mga panipi). Ang pag-uugali ay ang mga sumusunod:

Binabawasan ng LOOP ang ECX at sinusuri kung hindi zero ang ECX. Kung ang kundisyong iyon (zero) ay natugunan, ito ay tumalon sa isang tinukoy na label. Kung hindi, ito ay matatapos (magpatuloy sa iba pang mga tagubilin sa susunod na talakayan).

Binabawasan ng LOOPE ang ECX at sinusuri na ang ECX ay hindi zero (maaaring 1 halimbawa) at ang ZF ay nakatakda (sa 1). Kung matugunan ang mga kundisyong ito, tumalon ito sa label. Kung hindi, ito ay bumagsak.

Binabawasan ng LOOPNE ang ECX at sinusuri kung ang ECX ay hindi zero at ang ZF ay HINDI nakatakda (ibig sabihin, maging zero). Kung ang mga kundisyong ito ay natutugunan, ito ay tumalon sa label. Kung hindi, ito ay bumagsak.

Sa x64, ang RCX register o ang mga sub parts nito tulad ng ECX o CX, ay may hawak na counter integer. Gamit ang mga tagubilin sa LOOP, ang counter ay karaniwang nagbibilang pababa, bumababa ng 1 para sa bawat pagtalon (loop). Sa sumusunod na looping code segment, ang numero sa EAX register ay tumataas mula 0 hanggang 10 sa sampung pag-ulit habang ang numero sa ECX ay bumibilang (mga pagbabawas) nang 10 beses (basahin ang mga komento):

MOV EAX, 0 ;

MOV ECX, 10 ; bilang default ng 10 beses, isang beses para sa bawat pag-ulit

label:

INC EAX ; dagdagan ang EAX bilang loop body

LOOP label ; bawasan ang EAX, at kung ang EAX ay hindi zero, muling isagawa ang loop body mula sa 'label:'

Ang loop coding ay nagsisimula sa 'label:'. Pansinin ang paggamit ng colon. Ang loop coding ay nagtatapos sa 'LOOP label' na nagsasabing pagbabawas ng EAX. Kung ang nilalaman nito ay hindi zero, bumalik sa pagtuturo pagkatapos ng 'label:' at muling isagawa ang anumang pagtuturo (lahat ng mga tagubilin sa katawan) na bumababa hanggang sa 'LOOP label'. Tandaan na ang 'label' ay maaari pa ring magkaroon ng ibang pangalan.

6.36 Input/Output ng x64

Ang seksyong ito ng kabanata ay tumatalakay sa pagpapadala ng data sa isang output (internal) na port o pagtanggap ng data mula sa isang input (internal) na port. Ang chipset ay may walong-bit na port. Anumang dalawang magkasunod na 8-bit port ay maaaring ituring bilang isang 16-bit port, at anumang apat na magkakasunod na port ay maaaring maging isang 32-bit port. Sa ganitong paraan, maaaring ilipat ng processor ang 8, 16, o 32 bits papunta o mula sa isang panlabas na device.

Ang impormasyon ay maaaring ilipat sa pagitan ng processor at isang panloob na port sa dalawang paraan: gamit ang tinatawag na memory-mapped input/output o gamit ang isang hiwalay na input/output address space. Ang memory-mapped I/O ay katulad ng nangyayari sa 6502 processor kung saan ang mga port address ay talagang bahagi ng buong memory space. Sa kasong ito, kapag nagpapadala ng data sa isang partikular na lokasyon ng address, napupunta ito sa isang port at hindi sa isang memory bank. Maaaring may hiwalay na espasyo ng I/O address ang mga port. Sa huling kaso na ito, ang lahat ng mga memory bank ay may kanilang mga address mula sa zero. Mayroong hiwalay na hanay ng address mula 0000H hanggang FFFF16. Ang mga ito ay ginagamit ng mga port sa chipset. Ang motherboard ay naka-program upang hindi malito sa pagitan ng memory-mapped I/O at hiwalay na I/O address space.

Memory-Mapped I/O

Sa pamamagitan nito, ang mga port ay itinuturing na mga lokasyon ng memorya, at ang mga normal na opcode na gagamitin sa pagitan ng memorya at µP ay ginagamit para sa paglipat ng data sa pagitan ng µP at mga port. Kaya, upang ilipat ang isang byte mula sa isang port sa address na F000H patungo sa µP register na RAX:EAX:AX:AL, gawin ang sumusunod:

MOV AL, [F000H]

Ang isang string ay maaaring ilipat mula sa memorya sa isang port at vice-versa. Halimbawa:

MOVS [F000H], [C000H] ; ang source ay C000H, at ang destinasyon ay port sa F000H.

Paghiwalayin ang I/O Address Space

Sa pamamagitan nito, kailangang gamitin ang mga espesyal na tagubilin para sa input at output.

Paglilipat ng mga Iisang Item

Ang rehistro ng processor para sa paglipat ay RAX. Sa totoo lang, ito ay RAX:EAX para sa doubleword, RAX:EAX:AX para sa salita, at RAX:EAX:AX:AL para sa byte. Kaya, upang ilipat ang isang byte mula sa isang port sa FFF0h, sa RAX:EAX:AX:AL, i-type ang sumusunod:

SA AL, [FFF0H]

Para sa reverse transfer, i-type ang sumusunod:

LABAS [FFF0H], AL

Kaya, para sa mga solong item, ang mga tagubilin ay IN at OUT. Ang port address ay maaari ding ibigay sa RDX:EDX:DX register.

Paglilipat ng mga String

Ang isang string ay maaaring ilipat mula sa memorya sa isang chipset port at vice-versa. Upang ilipat ang isang string mula sa isang port sa address na FFF0H patungo sa memorya, magsimula sa C100H, i-type ang:

INS [ESI], [DX]

na may parehong epekto tulad ng:

INS [EDI], [DX]

Dapat ilagay ng programmer ang two-byte port address ng FFF0H sa RDX:EDX:Dx register, at dapat ilagay ang two-byte address ng C100H sa RSI:ESI o RDI:EDI register. Para sa reverse transfer, gawin ang sumusunod:

INS [DX], [ESI]

na may parehong epekto tulad ng:

INS [DX], [EDI]

6.37 Ang Stack sa x64

Tulad ng 6502 processor, ang x64 processor ay mayroon ding stack sa RAM. Ang stack para sa x64 ay maaaring 2 16 = 65,536 bytes ang haba o maaari itong maging 2 32 = 4,294,967,296 bytes ang haba. Lumalaki din ito pababa. Kapag ang nilalaman ng isang rehistro ay itinulak sa stack, ang numero sa RSP stack pointer ay nababawasan ng 8. Tandaan na ang isang memory address para sa x64 ay 64 bits ang lapad. Ang halaga sa stack pointer sa µP ay tumuturo sa susunod na lokasyon sa stack sa RAM. Kapag ang nilalaman ng isang rehistro (o isang halaga sa isang operand) ay lumabas mula sa stack patungo sa isang rehistro, ang numero sa RSP stack pointer ay tataas ng 8. Ang operating system ay nagpapasya sa laki ng stack at kung saan ito magsisimula sa RAM at lumalaki pababa. Tandaan na ang stack ay isang Last-In-First-Out (LIFO) na istraktura na lumalaki pababa at lumiliit paitaas sa kasong ito.

Upang itulak ang nilalaman ng µP RBX na rehistro sa stack, gawin ang sumusunod:

PUSH RBX

Upang i-pop ang huling entry sa stack pabalik sa RBX, gawin ang sumusunod:

POP RBX

6.38 Pamamaraan sa x64

Ang subroutine sa x64 ay tinatawag na 'procedure'. Ang stack ay ginagamit dito nang higit pa kaysa sa ginamit para sa 6502 µP. Ang syntax para sa isang x64 procedure ay:

proc_name:

katawan ng pamamaraan

…

tama

Bago magpatuloy, pansinin na ang mga opcode at label para sa isang x64 subroutine (mga tagubilin sa wika ng assembly sa pangkalahatan) ay case insensitive. Iyon ay ang proc_name ay kapareho ng PROC_NAME. Tulad ng 6502, ang pangalan ng pangalan ng pamamaraan (label) ay nagsisimula sa simula ng isang bagong linya sa text editor para sa assembly language. Sinusundan ito ng colon at hindi ng space at opcode tulad ng sa 6502. Sumusunod ang subroutine body, na nagtatapos sa RET at hindi RTS gaya ng 6502 µP. Tulad ng 6502, ang bawat pagtuturo sa katawan, kabilang ang RET, ay hindi nagsisimula sa simula ng linya nito. Tandaan na ang isang label dito ay maaaring higit sa 8 character ang haba. Upang tawagan ang pamamaraang ito, mula sa itaas o ibaba ng na-type na pamamaraan, gawin ang sumusunod:

TUMAWAG proc_name

Gamit ang 6502, ang pangalan ng label ay uri lamang para sa pagtawag. Gayunpaman, dito, ang nakareserbang salitang 'TUMAWAG' o 'tawag' ay nai-type, na sinusundan ng pangalan ng pamamaraan (subroutine) pagkatapos ng isang puwang.

Kapag nakikitungo sa mga pamamaraan, karaniwang may dalawang pamamaraan. Ang isang pamamaraan ay tumatawag sa isa pa. Ang pamamaraan na tumatawag (may tagubilin sa tawag) ay tinatawag na 'tumatawag', at ang pamamaraan na tinatawag ay tinatawag na 'callee'. May convention (rules) na dapat sundin.

Mga Panuntunan ng Tumatawag

Dapat sumunod ang tumatawag sa mga sumusunod na panuntunan kapag gumagamit ng subroutine:

1. Bago tumawag ng subroutine, dapat na i-save ng tumatawag ang mga nilalaman ng ilang partikular na rehistro na itinalaga bilang caller-save sa stack. Ang mga rehistrong na-save ng tumatawag ay R10, R11, at anumang mga rehistro kung saan inilalagay ang mga parameter (RDI, RSI, RDX, RCX, R8, R9). Kung ang mga nilalaman ng mga rehistrong ito ay pananatilihin sa buong subroutine na tawag, itulak ang mga ito sa stack sa halip na i-save pagkatapos ay sa RAM. Ang mga ito ay kailangang gawin dahil ang mga rehistro ay kailangang gamitin ng tumatawag upang burahin ang mga naunang nilalaman.

2. Kung ang pamamaraan ay magdagdag ng dalawang numero halimbawa, ang dalawang numero ay ang mga parameter na ipapasa sa stack. Upang maipasa ang mga parameter sa subroutine, ilagay ang anim sa mga ito sa mga sumusunod na rehistro sa pagkakasunud-sunod: RDI, RSI, RDX, RCX, R8, R9. Kung mayroong higit sa anim na parameter sa subroutine, itulak ang natitira sa stack sa reverse order (ibig sabihin, huling parameter muna). Dahil bumababa ang stack, ang una sa mga dagdag na parameter (talagang ang ikapitong parameter) ay iniimbak sa pinakamababang address (ang pagbabalik-tanaw na ito ng mga parameter ay dating ginamit upang payagan ang mga function (subroutine) na maipasa na may variable na bilang ng mga parameter).

3. Para tawagan ang subroutine (procedure), gamitin ang call instruction. Inilalagay ng tagubiling ito ang return address sa itaas ng mga parameter sa stack (pinakamababang posisyon) at ang mga branch sa subroutine code.

4. Pagkatapos bumalik ang subroutine (ibig sabihin, kaagad na sumusunod sa pagtuturo ng tawag), dapat alisin ng tumatawag ang anumang karagdagang parameter (lampas sa anim na nakaimbak sa mga rehistro) mula sa stack. Ibinabalik nito ang stack sa estado nito bago isagawa ang tawag.

5. Maaaring asahan ng tumatawag na mahanap ang return value (address) ng subroutine sa RAX register.

6. Ibinabalik ng tumatawag ang mga nilalaman ng mga rehistrong na-save ng tumatawag (R10, R11, at anuman sa mga parameter na nagpapasa ng mga rehistro) sa pamamagitan ng paglabas ng mga ito sa stack. Maaaring ipagpalagay ng tumatawag na walang ibang mga rehistro ang binago ng subroutine.

Dahil sa paraan ng pagkakabalangkas ng calling convention, kadalasan ang ilan (o karamihan) sa mga hakbang na ito ay hindi gagawa ng anumang pagbabago sa stack. Halimbawa, kung mayroong anim o mas kaunting mga parameter, walang itinutulak sa stack sa hakbang na iyon. Gayundin, ang mga programmer (at mga compiler) ay karaniwang pinapanatili ang mga resulta na pinapahalagahan nila mula sa mga rehistro na naka-save ng tumatawag sa mga hakbang 1 at 6 upang maiwasan ang labis na mga push at pop.

Mayroong dalawang iba pang mga paraan ng pagpasa ng mga parameter sa isang subroutine, ngunit ang mga iyon ay hindi tatalakayin sa online na kurso sa karera. Ang isa sa kanila ay gumagamit ng stack mismo sa halip na ang pangkalahatang layunin na mga rehistro.

Mga Panuntunan ng Callee

Ang kahulugan ng tinatawag na subroutine ay dapat sumunod sa mga sumusunod na patakaran:

1. Ilaan ang mga lokal na variable (mga variable na binuo sa loob ng pamamaraan) gamit ang mga rehistro o paggawa ng espasyo sa stack. Alalahanin na ang stack ay lumalaki pababa. Kaya, upang makagawa ng espasyo sa tuktok ng stack, dapat na bawasan ang stack pointer. Ang halaga kung saan binabawasan ang stack pointer ay depende sa kinakailangang bilang ng mga lokal na variable. Halimbawa, kung kinakailangan ang isang lokal na float at isang lokal na haba (kabuuan ng 12 bytes), kailangang bawasan ng 12 ang stack pointer upang makagawa ng espasyo para sa mga lokal na variable na ito. Sa isang mataas na antas ng wika tulad ng C, nangangahulugan ito na ideklara ang mga variable nang hindi nagtatalaga (nagsisimula) ng mga halaga.

2. Susunod, ang mga halaga ng anumang mga rehistro na ang itinalagang callee-save (pangkalahatang layunin na mga rehistro na hindi na-save ng tumatawag) na ginagamit ng function ay dapat na i-save. Upang i-save ang mga rehistro, itulak ang mga ito sa stack. Ang mga rehistrong na-save ng callee ay RBX, RBP, at R12 hanggang R15 (Pinapanatili din ang RSP ng convention ng tawag, ngunit hindi kailangang itulak sa stack sa hakbang na ito).

Matapos maisagawa ang tatlong pagkilos na ito, maaaring magpatuloy ang aktwal na operasyon ng subroutine. Kapag handa nang bumalik ang subroutine, magpapatuloy ang mga panuntunan sa call convention.

3. Kapag tapos na ang subroutine, dapat ilagay sa RAX ang return value para sa subroutine kung wala pa ito.

4. Dapat na ibalik ng subroutine ang mga lumang halaga ng anumang mga rehistrong na-save ng callee (RBX, RBP, at R12 hanggang R15) na binago. Ang mga nilalaman ng rehistro ay naibalik sa pamamagitan ng pag-pop ang mga ito mula sa stack. Tandaan na ang mga rehistro ay dapat na i-pop sa kabaligtaran na pagkakasunud-sunod na sila ay itinulak.

5. Susunod, i-deallocate namin ang mga lokal na variable. Ang pinakamadaling paraan upang gawin ito ay idagdag sa RSP ang parehong halaga na ibinawas dito sa hakbang 1.

6. Sa wakas, bumalik tayo sa tumatawag sa pamamagitan ng pagsasagawa ng ret instruction. Hahanapin at aalisin ng tagubiling ito ang naaangkop na return address mula sa stack.

Ang isang halimbawa ng katawan ng isang subroutine ng tumatawag upang tumawag sa isa pang subroutine na 'myFunc' ay ang mga sumusunod (basahin ang mga komento):

; Gustong tumawag sa isang function na 'myFunc' na tumatagal ng tatlo

; integer na parameter. Ang unang parameter ay nasa RAX .

; Ang pangalawang parameter ay ang pare-pareho 456. Pangatlo

; ang parameter ay nasa lokasyon ng memorya na 'variabl'

itulak rdi; rdi ay magiging isang param , kaya i-save ito

; long retVal = myFunc ( x , 456 , z ) ;

mov rdi, rax; ilagay ang unang parameter sa RDI

mov rsi, 456; ilagay ang pangalawang parameter sa RSI

mov rdx , [variabl] ; ilagay ang ikatlong parameter sa RDX

tawagan ang myFunc ; tawagan ang function

pop rdi ; ibalik ang naka-save na halaga ng RDI

; ang return value ng myFunc ay available na ngayon sa RAX

Ang isang halimbawa ng callee function (myFunc) ay (basahin ang mga komento):

myFunc :

; ∗∗∗ Standard subroutine prologue ∗∗∗

sub rsp, 8; silid para sa isang 64−bit na lokal na variable (resulta) gamit ang 'sub' na opcode

itulak ang rbx; save callee−save registers

itulak ang rbp; parehong gagamitin ng myFunc

; ∗∗∗ Sub routine Katawan ∗∗∗

mov rax, rdi; parameter 1 hanggang RAX

mov rbp, rsi; parameter 2 hanggang RBP

mov rbx , rdx ; parameter 3 hanggang rb x

mov [ rsp + 1 6 ] , rbx ; ilagay ang rbx sa lokal na variable

magdagdag ng [ rsp + 1 6 ] , rbp ; magdagdag ng rbp sa lokal na variable

mov rax , [ rsp +16 ] ; mov na nilalaman ng lokal na variable sa RAX

; (return value/final result)

; ∗∗∗ Karaniwang subroutine epilogue ∗∗∗

pop rbp; mabawi ang callee save registers

pop rbx ; baliktad ng kapag tinulak

magdagdag ng rsp, 8; i-deloklocate ang (mga) lokal na variable. Ang ibig sabihin ng 8 ay 8 bytes

ret ; pop top value mula sa stack , tumalon doon

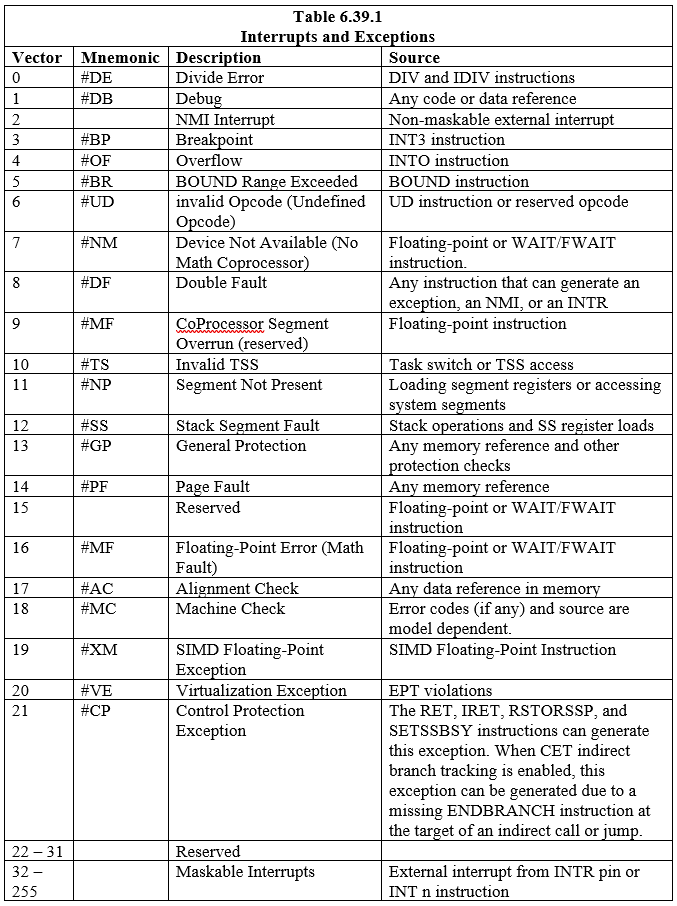

6.39 Mga Interrupt at Exceptions para sa x64

Ang processor ay nagbibigay ng dalawang mekanismo para sa pag-abala sa pagpapatupad ng programa, mga pagkagambala, at mga pagbubukod:

- Ang interrupt ay isang asynchronous (maaaring mangyari anumang oras) na kaganapan na karaniwang na-trigger ng isang I/O device.

- Ang isang exception ay isang kasabay na kaganapan (nangyayari habang ang code ay naisakatuparan, na-pre-program, batay sa ilang pangyayari) na nabuo kapag ang processor ay nakakita ng isa o higit pang mga paunang natukoy na kundisyon habang nagsasagawa ng isang pagtuturo. Tatlong klase ng mga pagbubukod ang tinukoy: mga fault, traps, at abort.

Ang processor ay tumutugon sa mga pagkagambala at mga pagbubukod sa mahalagang parehong paraan. Kapag may na-signal na interrupt o exception, ihihinto ng processor ang pagpapatupad ng kasalukuyang programa o gawain at lilipat sa pamamaraan ng handler na partikular na isinulat upang mahawakan ang kondisyon ng interrupt o exception. Ina-access ng processor ang pamamaraan ng handler sa pamamagitan ng isang entry sa Interrupt Descriptor Table (IDT). Kapag natapos na ng handler ang paghawak sa interrupt o exception, ibabalik ang kontrol ng program sa naantala na programa o gawain.

Karaniwang pinangangasiwaan ng operating system, executive, at/o device driver ang mga pagkaantala at pagbubukod nang independyente mula sa mga application program o mga gawain. Gayunpaman, maa-access ng mga application program ang mga humahawak ng interrupt at exception na kasama sa isang operating system o ipapatupad ito sa pamamagitan ng mga tawag sa assembly-language.

Labingwalong (18) paunang-natukoy na mga interrupt at exception, na nauugnay sa mga entry sa IDT, ay tinukoy. Ang dalawang-daang dalawampu't apat (224) na mga interrupt na tinukoy ng gumagamit ay maaari ding gawin at iugnay sa talahanayan. Ang bawat interrupt at exception sa IDT ay tinutukoy ng isang numero na tinatawag na 'vector'. Inililista ng Talahanayan 6.39.1 ang mga interrupt at exception na may mga entry sa IDT at kani-kanilang mga vector. Ang mga Vector 0 hanggang 8, 10 hanggang 14, at 16 hanggang 19 ay ang mga paunang natukoy na interrupt at exception. Ang mga vectors 32 hanggang 255 ay para sa software-defined interrupts (user) na para sa alinman sa software interrupts o maskable hardware interrupts.

Kapag nakakita ang processor ng isang interrupt o exception, ginagawa nito ang isa sa mga sumusunod na bagay:

- Magsagawa ng implicit na tawag sa isang pamamaraan ng handler

- Magsagawa ng implicit na tawag sa isang handler na gawain

6.4 Ang 64-Bit na ARM na Mga Pangunahing Kaalaman sa Arkitektura ng Computer

Ang mga arkitektura ng ARM ay tumutukoy sa isang pamilya ng mga processor ng RISC na angkop para sa paggamit sa iba't ibang uri ng mga application. Ang ARM ay isang arkitektura ng pag-load/store na nangangailangan ng data na mai-load mula sa memorya patungo sa isang rehistro bago ang anumang pagpoproseso tulad ng isang operasyon ng ALU (Arithmetic Logic Unit) ay maaaring maganap kasama nito. Ang isang kasunod na pagtuturo ay nag-iimbak ng resulta pabalik sa memorya. Bagama't ito ay tila isang hakbang pabalik mula sa x86 at x64 na mga arkitektura, na direktang gumagana sa mga operand sa memorya sa isang pagtuturo (gamit ang mga rehistro ng processor, siyempre), ang diskarte sa pag-load/store, sa pagsasanay, ay nagbibigay-daan sa ilang mga sunud-sunod na operasyon. na maisagawa sa mataas na bilis sa isang operand kapag na-load ito sa isa sa maraming mga rehistro ng processor. Ang mga processor ng ARM ay may opsyon ng little endianness o big-endianness. Ang default na setting ng ARM 64 ay little-endian na siyang configuration na karaniwang ginagamit ng mga operating system. Ang 64-bit na arkitektura ng ARM ay moderno at nakatakda itong palitan ang 32-bit na arkitektura ng ARM.

Tandaan : Ang bawat tagubilin para sa 64-bit ARM µP ay 4 bytes (32 bits) ang haba.

6.41 Ang 64-Bit ARM Register Set

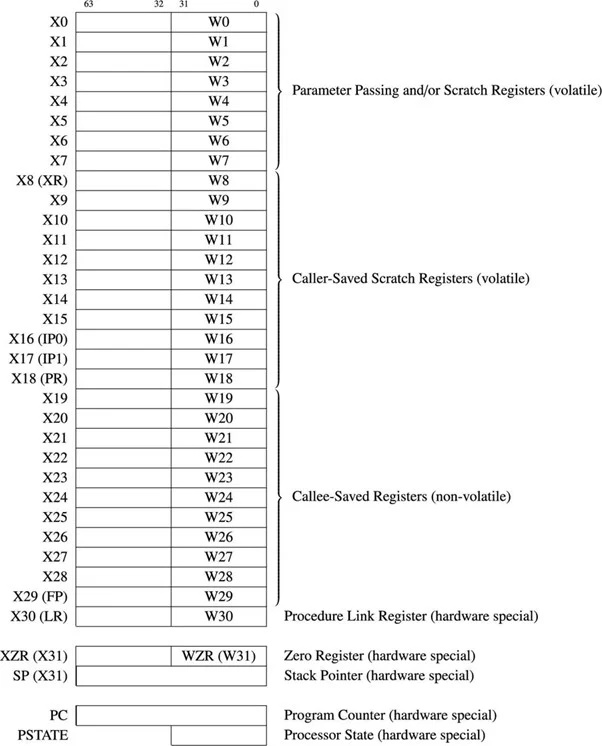

Mayroong 31 pangkalahatang layunin ng 64-bit na mga rehistro para sa 64-bit na ARM µP. Ang sumusunod na diagram ay nagpapakita ng pangkalahatang layunin na mga rehistro at ilang mahahalagang rehistro:

Fig.4.11.1 64-Bit na Pangkalahatang Layunin at Ilang Mahahalagang Rehistro

Ang mga rehistro ng pangkalahatang layunin ay tinutukoy bilang X0 hanggang X30. Ang unang 32-bit na bahagi para sa bawat rehistro ay tinutukoy bilang W0 hanggang W30. Kapag ang pagkakaiba sa pagitan ng 32 bits at 64 bits ay hindi binigyang-diin, ang 'R' prefix ay ginagamit. Halimbawa, ang R14 ay tumutukoy sa W14 o X14.

Ang 6502 µP ay may 16-bit na Programa Counter at maaaring tugunan ang 2 16 mga lokasyon ng memory byte. Ang 64-bit ARM µP ay may 64-bit na Programa Counter at maaaring tumugon ng hanggang 2 64 = 1.844674407 x 1019 (talagang 18,446,744,073,709,551,616) mga lokasyon ng memory byte. Hawak ng program counter ang address ng susunod na pagtuturo na isasagawa. Ang haba ng pagtuturo ng ARM64 o AArch64 ay karaniwang apat na byte. Awtomatikong dinadagdagan ng processor ang rehistrong ito ng apat pagkatapos makuha ang bawat pagtuturo mula sa memorya.

Ang Stack Pointer register o SP ay hindi kabilang sa 31 general purpose registers. Ang stack pointer ng anumang arkitektura ay tumuturo sa huling stack entry sa memorya. Para sa ARM-64, ang stack ay lumalaki pababa.

Ang 6502 µP ay may 8-bit na Processor Status Register. Ang katumbas sa ARM64 ay tinatawag na PSTATE register. Ang rehistrong ito ay nag-iimbak ng mga flag na ginagamit para sa mga resulta ng mga operasyon at para sa pagkontrol sa processor (µP). Ito ay 32-bits ang lapad. Ang sumusunod na talahanayan ay nagbibigay ng mga pangalan, index, at mga kahulugan para sa karaniwang ginagamit na mga bit sa rehistro ng PSTATE:

| Talahanayan 6.41.1 Pinaka Ginamit na Mga Flag ng PSTATE (Bit) |

||

|---|---|---|

| Simbolo | bit | Layunin |

| M | 0-3 | Mode: Ang kasalukuyang antas ng pribilehiyo sa pagpapatupad (USR, SVC, at iba pa). |

| T | 4 | Thumb: Ito ay nakatakda kung ang set ng pagtuturo ng T32 (Thumb) ay aktibo. Kung malinaw, aktibo ang set ng pagtuturo ng ARM. Maaaring itakda at i-clear ng user code ang bit na ito. |

| AT | 9 | Endianness: Ang pagtatakda ng bit na ito ay nagbibigay-daan sa big-endian mode. Kung malinaw, aktibo ang little-endian mode. Ang default ay ang little-endian mode. |

| Q | 27 | Cumulative saturation flag: Ito ay nakatakda kung, sa ilang mga punto sa isang serye ng mga operasyon, isang overflow o saturation ay magaganap |

| SA | 28 | Overflow flag: Ito ay nakatakda kung ang operasyon ay nagresulta sa isang nilagdaang overflow. |

| C | 29 | Carry flag: Ito ay nagpapahiwatig kung ang karagdagan ay nagdulot ng isang carry o ang pagbabawas ay nagbunga ng isang hiram. |

| SA | 30 | Zero flag: Ito ay nakatakda kung ang resulta ng isang operasyon ay zero. |

| N | 31 | Negative flag: Ito ay nakatakda kung ang resulta ng isang operasyon ay negatibo. |

Ang ARM-64 µP ay may maraming iba pang mga rehistro.

SIMD

SIMD ay kumakatawan sa Single Instruction, Multiple Data. Nangangahulugan ito na ang isang pagtuturo ng wika ng pagpupulong ay maaaring kumilos sa maraming data nang sabay sa isang microprocessor. Mayroong tatlumpu't dalawang 128 bits na malawak na rehistro para gamitin sa SIMD at mga floating-point na operasyon.

6.42 Memory Mapping

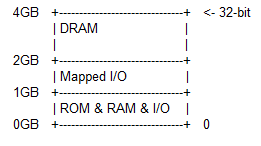

Ang RAM at DRAM ay parehong Random Access Memories. Ang DRAM ay mas mabagal sa operasyon kaysa sa RAM. Ang DRAM ay mas mura kaysa sa RAM. Kung mayroong higit sa 32 gigabyte (GB) ng patuloy na DRAM sa memorya, magkakaroon ng higit pang mga problema sa pamamahala ng memorya: 32 GB = 32 x 1024 x 1024 x 1024 bytes. Para sa isang buong memory space na mas malaki kaysa sa 32 GB, ang DRAM na higit sa 32 GB ay dapat na interspersed sa mga RAM para sa mas mahusay na pamamahala ng memorya. Upang maunawaan ang ARM-64 memory map, dapat mo munang maunawaan ang 4GB memory map para sa 32-bit ARM Central Processing Unit (CPU). Ang ibig sabihin ng CPU ay µP. Para sa isang 32-bit na computer, ang maximum na memory addressable space ay 2 32 = 4 x 2 10 x 2 10 x 2 10 = 4 x 1024 x 1024 x 1024 = 4,294,967,296 = 4GB.

32-Bit na ARM Memory Map

Ang memory map para sa isang 32-bit na ARM ay:

Para sa isang 32-bit na computer, ang maximum na laki ng buong memorya ay 4GB. Mula sa 0GB na address hanggang sa 1GB na address ay ang ROM Operating System, RAM, at mga lokasyon ng I/O. Ang buong ideya ng ROM OS, RAM, at I/O address ay katulad ng sitwasyon ng Commodore-64 na may posibleng 6502 CPU. Ang OS ROM para sa Commodore-64 ay nasa tuktok na dulo ng memory space. Ang ROM OS dito ay mas malaki kaysa sa Commodore-64, at ito ay nasa simula ng buong memory address space. Kung ihahambing sa iba pang modernong mga computer, ang ROM OS dito ay kumpleto, sa kahulugan na ito ay maihahambing sa dami ng OS sa kanilang mga hard drive. Mayroong dalawang pangunahing dahilan sa pagkakaroon ng OS sa mga integrated circuit ng ROM: 1) Ang mga ARM CPU ay kadalasang ginagamit sa maliliit na device tulad ng mga smartphone. Maraming hard drive ang mas malaki kaysa sa mga smartphone at iba pang maliliit na devise, 2) para sa seguridad. Kapag ang OS ay nasa Read Only memory, hindi ito ma-corrupt (mga bahaging na-overwrit) ng mga hacker. Ang mga seksyon ng RAM at mga seksyon ng input/output ay napakalaki rin kumpara sa mga bahagi ng Commodore-64.

Kapag ang kapangyarihan ay inilagay sa 32-bit ROM OS, ang OS ay dapat magsimula sa (boot mula) sa 0x00000000 address o 0xFFFF0000 address kung ang mga HiVEC ay pinagana. Kaya, kapag ang kapangyarihan ay inilagay pagkatapos ng reset phase, ang CPU hardware ay naglo-load ng 0x00000000 o 0xFFFF0000 sa Program Counter. Ang prefix na '0x' ay nangangahulugang Hexadecimal. Ang boot address ng ARMv8 64bit na mga CPU ay isang tinukoy na pagpapatupad. Gayunpaman, pinapayuhan ng may-akda ang computer engineer na magsimula sa 0x00000000 o 0xFFFF0000 para sa kapakanan ng backward compatibility.

Mula 1GB hanggang 2GB ay ang naka-map na input/output. May pagkakaiba sa pagitan ng naka-map na I/O at I/O lang na matatagpuan sa pagitan ng 0GB at 1GB. Sa I/O, ang address para sa bawat port ay naayos tulad ng sa Commodore-64. Sa naka-map na I/O, ang address para sa bawat port ay hindi palaging pareho para sa bawat operasyon ng computer (dynamic).

Mula 2GB hanggang 4GB ay DRAM. Ito ang inaasahang (o karaniwan) na RAM. Ang DRAM ay kumakatawan sa Dynamic RAM, hindi ang kahulugan ng pagbabago ng address sa panahon ng operasyon ng computer ngunit sa kahulugan na ang halaga ng bawat cell sa pisikal na RAM ay kailangang i-refresh sa bawat pulso ng orasan.

Tandaan :

- Mula 0x0000,0000 hanggang 0x0000, ang FFFF ay ang OS ROM.

- Mula 0x0001,0000 hanggang 0x3FFF,FFFF, maaaring magkaroon ng higit pang ROM, pagkatapos ay RAM, at pagkatapos ay ilang I/O.

- Mula 0x4000,0000 hanggang 0x7FFF, FFFF, pinapayagan ang karagdagang I/O at/o naka-map na I/O.

- Mula 0x8000,0000 hanggang 0xFFFF, FFFF ang inaasahang DRAM.

Nangangahulugan ito na ang inaasahang DRAM ay hindi kailangang magsimula sa 2GB na hangganan ng memorya, sa pagsasanay. Bakit dapat igalang ng programmer ang mga ideal na hangganan kapag walang sapat na pisikal na RAM na mga bangko na nakalagay sa motherboard? Ito ay dahil ang customer ay walang sapat na pera para sa lahat ng mga bangko ng RAM.

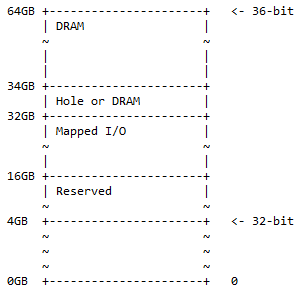

36-Bit na ARM Memory Map

Para sa isang 64-bit ARM computer, ang lahat ng 32 bits ay ginagamit upang matugunan ang buong memorya. Para sa isang 64-bit ARM computer, ang unang 36 bits ay maaaring gamitin upang tugunan ang buong memorya na, sa kasong ito, ay 2 36 = 68,719,476,736 = 64GB. Marami na itong alaala. Ang mga ordinaryong computer ngayon ay hindi nangangailangan ng ganitong halaga ng memorya. Hindi pa ito hanggang sa maximum na hanay ng memorya na maaaring ma-access ng 64 bits. Ang memory map para sa 36-bits para sa ARM CPU ay:

Mula sa 0GB address hanggang sa 4GB na address ay ang 32-bit memory map. Ang ibig sabihin ng 'Nakareserba' ay hindi nagamit at pinananatili para magamit sa hinaharap. Hindi kailangang maging mga pisikal na memory bank na naka-slot sa motherboard para sa espasyong iyon. Dito, ang DRAM at naka-map na I/O ay may parehong kahulugan tulad ng para sa 32-bit na memory map.

Ang sumusunod na sitwasyon ay maaaring matagpuan sa pagsasanay:

- 0x1 0000 0000 – 0x3 FFFF FFFF; nakalaan. 12GB ng address space ay nakalaan para magamit sa hinaharap.

- 0x4 0000 0000 – 0x7 FFFF FFFF; nakamapang I/O. Available ang 16GB ng address space para sa dynamic na nakamapang I/O.

- 0x8 0000 0000 – 0x8 7FFF FFFF FFFF; Hole o DRAM. Ang 2GB ng address space ay maaaring maglaman ng alinman sa mga sumusunod:

- Hole para paganahin ang DRAM device partitioning (tulad ng inilarawan sa sumusunod na talakayan).

- DRAM.

- 0x8 8000 0000 – 0xF FFFF FFFF; DRAM. 30GB ng address space para sa DRAM.

Ang memory map na ito ay isang superset ng 32-bit address map, na ang karagdagang espasyo ay nahahati bilang 50% DRAM (1/2) na may opsyonal na butas dito at 25% na naka-map na I/O space at nakalaan na espasyo (1/4). ). Ang natitirang 25% (1/4) ay para sa 32-bit memory map ½ + ¼ + ¼ = 1.

Tandaan : Mula sa 32 bits hanggang 360 bits ay isang karagdagan ng 4 bits sa pinaka makabuluhang bahagi ng 36 bits.

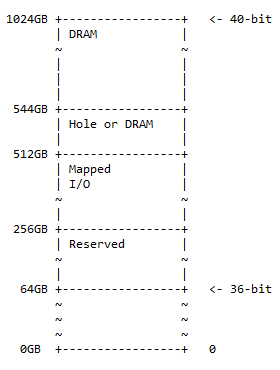

40-Bit Memory Map

Ang 40-bit address map ay isang superset ng 36-bit na address map at sumusunod sa parehong pattern ng 50% DRAM ng isang opsyonal na butas sa loob nito, 25% na naka-map na I/O space at reserved space, at ang natitira sa 25% puwang para sa nakaraang memory map (36-bit). Ang diagram para sa memory map ay:

Ang laki ng butas ay 544 – 512 = 32GB. Ang sumusunod na sitwasyon ay maaaring matagpuan sa pagsasanay:

- 0x10 0000 0000 – 0x3F FFFF FFFF; nakalaan. 192GB ng address space ay nakalaan para magamit sa hinaharap.

- 0x40 0000 0000 – 0x7F FFFF FFFF; nakamapa. I/O 256GB ng address space ay available para sa dynamic na nakamapang I/O.

- 0x80 0000 0000 – 0x87 FFFF FFFF; butas o DRAM. Ang 32GB ng address space ay maaaring maglaman ng alinman sa mga sumusunod:

- Hole para paganahin ang DRAM device partitioning (tulad ng inilarawan sa sumusunod na talakayan)

- DRAM

- 0x88 0000 0000 – 0xFF FFFF FFFF; DRAM. 480GB ng address space para sa DRAM.

Tandaan : Mula sa 36 bits hanggang 40 bits ay isang karagdagan ng 4 bits sa pinaka makabuluhang bahagi ng 36 bits.

DRAM Hole

Sa memory map na lampas sa 32-bits, ito ay alinman sa isang DRAM Hole o isang pagpapatuloy ng DRAM mula sa itaas. Kapag ito ay isang butas, ito ay dapat pahalagahan tulad ng sumusunod: Ang DRAM hole ay nagbibigay ng paraan upang hatiin ang isang malaking DRAM device sa maraming hanay ng address. Ang opsyonal na butas ng DRAM ay iminungkahi sa simula ng mas mataas na hangganan ng DRAM address. Nagbibigay-daan ito sa isang pinasimpleng decoding scheme kapag naghahati ng malaking kapasidad na DRAM device sa mas mababang rehiyong pisikal na tinutugunan.

Halimbawa, ang isang 64GB na bahagi ng DRAM ay nahahati sa tatlong rehiyon kung saan ang mga address offset ay ginawa sa pamamagitan ng isang simpleng pagbabawas sa mga high order na bits ng address tulad ng sumusunod:

| Talahanayan 6.42.1 Halimbawa ng 64GB DRAM Partitioning with Holes |

|||

|---|---|---|---|

| Mga Pisikal na Address sa SoC | Offset | Panloob na DRAM address | |

| 2 GBytes (32-bit na mapa) | 0x00 8000 0000 – 0x00 FFFF FFFF | -0x00 8000 0000 | 0x00 0000 0000 – 0x00 7FFF FFFF |

| 30 GBytes (36-bit na mapa) | 0x08 8000 0000 – 0x0F FFFF FFFF | -0x08 0000 0000 | 0x00 8000 0000 – 0x07 FFFF FFFF |

| 32 GBytes (40-bit na mapa) | 0x88 0000 0000 – 0x8F FFFF FFFF | -0x80 0000 0000 | 0x08 0000 0000 – 0x0F FFFF FFFF |

Iminungkahing 44-Bit at 48-Bit Addressed Memory Maps para sa mga ARM CPU

Ipagpalagay na ang isang Personal na Computer ay may 1024GB (= 1TB) ng memorya; iyon ay masyadong maraming memorya. Kaya, ang 44-bit at 48-bit na mga mapa ng memorya na naka-address para sa mga ARM CPU para sa 16 TB at 256 TB, ayon sa pagkakabanggit, ay mga panukala lamang para sa hinaharap na mga pangangailangan ng computer. Sa katunayan, ang mga panukalang ito para sa mga ARM CPU ay sumusunod sa parehong dibisyon ng memorya ayon sa ratio gaya ng mga naunang mapa ng memorya. Iyon ay: 50% DRAM na may opsyonal na butas sa loob nito, 25% na naka-map na I/O space at nakalaan na espasyo, at ang natitirang bahagi ng 25% na espasyo para sa nakaraang memory map.

Ang 52-bit, 56-bit, 60-bit at 64-bit addressed memory map ay imumungkahi pa rin para sa ARM 64 bits para sa malayong hinaharap. Kung nakita pa rin ng mga siyentipiko sa oras na iyon na kapaki-pakinabang ang 50 : 25 : 25 partitioning ng buong memory space, pananatilihin nila ang ratio.

Tandaan : Ang SoC ay nangangahulugang System-on-Chip na tumutukoy sa mga circuit sa µP chip na kung hindi man ay wala doon.

Ang SRAM o Static Random Access Memory ay mas mabilis kaysa sa mas tradisyonal na DRAM, ngunit nangangailangan ng mas maraming lugar ng silicon. Ang SRAM ay hindi nangangailangan ng pag-refresh. Maaaring isipin ng mambabasa ang RAM bilang SRAM.

6.43 Assembly Language Addressing Modes para sa ARM 64

Ang ARM ay isang arkitektura ng pag-load/store na nangangailangan ng data na mai-load mula sa memorya patungo sa isang rehistro ng processor bago maganap ang anumang pagproseso tulad ng Arithmetic Logic Operation kasama nito. Ang isang kasunod na pagtuturo ay nag-iimbak ng resulta pabalik sa memorya. Bagama't ito ay tila isang hakbang pabalik mula sa x86 at sa mga kasunod nitong x64 na mga arkitektura, na direktang gumagana sa mga operand sa memorya sa isang pagtuturo, sa pagsasagawa, ang diskarte sa pag-load/store ay nagpapahintulot sa ilang sunud-sunod na operasyon na maisagawa sa mataas na bilis sa isang operand kapag na-load ito sa isa sa maraming mga rehistro ng processor.

Ang format ng ARM assembly language ay may pagkakatulad at pagkakaiba sa x64 (x86) series.

- Offset : Ang isang pinirmahang constant ay maaaring idagdag sa base register. Ang offset ay nai-type bilang bahagi ng pagtuturo. Halimbawa: ang ldr x0, [rx, #10] ay naglo-load ng r0 ng salita sa r1+10 address.

- Magrehistro : Ang isang unsigned increment na nakaimbak sa isang rehistro ay maaaring idagdag o ibawas mula sa halaga sa isang base register. Halimbawa: ang ldr r0, [x1, x2] ay naglo-load ng r0 ng salita sa x1+x2 address. Ang alinman sa mga rehistro ay maaaring isipin bilang base na rehistro.

- Naka-scale na rehistro : Ang isang pagtaas sa isang rehistro ay inilipat pakaliwa o pakanan sa pamamagitan ng isang tinukoy na bilang ng mga bit na posisyon bago idagdag o ibawas mula sa base na halaga ng rehistro. Halimbawa: ang ldr x0, [x1, x2, lsl #3] ay naglo-load ng r0 ng salita sa r1+(r2×8) address. Ang shift ay maaaring isang lohikal na left o right shift (lsl o lsr) na naglalagay ng zero bits sa mga nabakanteng posisyon ng bit o isang arithmetic right shift (asr) na kinokopya ang sign bit sa mga nabakanteng posisyon.

Kapag may dalawang operand, ang patutunguhan ay nauuna (sa kaliwa) ang pinagmulan (may ilang mga pagbubukod dito). Ang mga opcode para sa ARM assembly language ay case insensitive.

Agarang ARM64 Addressing Mode

Halimbawa:

mov r0, #0xFF000000 ; I-load ang 32-bit na halaga FF000000h sa r0

Ang isang decimal na halaga ay walang 0x ngunit nauunahan pa rin ng #.

Direktang Magrehistro

Halimbawa:

mov x0, x1 ; Kopyahin ang x1 hanggang x0

Hindi Direktang Magrehistro

Halimbawa:

str x0, [x3] ; Itabi ang x0 sa address sa x3

Magrehistro Hindi Direkta gamit ang Offset

Mga halimbawa:

ldr x0, [x1, #32] ; I-load ang r0 na may halaga sa address [r1+32]; r1 ang base register

str x0, [x1, #4] ; Itabi ang r0 sa address [r1+4]; r1 ay ang batayang rehistro; ang mga numero ay base 10

Hindi Direktang Magrehistro gamit ang Offset (Pre-incremented)

Mga halimbawa:

ldr x0, [x1, #32]! ; I-load ang r0 gamit ang [r1+32] at i-update ang r1 sa (r1+32)

str x0, [x1, #4]! ; I-store ang r0 sa [r1+4] at i-update ang r1 sa (r1+4)

Pansinin ang paggamit ng “!” simbolo.

Magrehistro Hindi Direkta gamit ang Offset (Post-incremented)

Mga halimbawa:

ldr x0, [x1], #32 ; I-load ang [x1] sa x0, pagkatapos ay i-update ang x1 sa (x1+32)

str x0, [x1], #4 ; I-store ang x0 sa [x1], pagkatapos ay i-update ang x1 sa (x1+4)

Hindi Direktang Double Register

Ang address ng operand ay ang kabuuan ng base register at increment register. Ang mga pangalan ng rehistro ay napapalibutan ng mga square bracket.

Mga halimbawa:

ldr x0, [x1, x2] ; I-load ang x0 gamit ang [x1+x2]

str x0, [rx, x2] ; I-store ang x0 hanggang [x1+x2]

Relative Addressing Mode

Sa relative addressing mode, ang mabisang pagtuturo ay ang susunod na pagtuturo sa Program Counter, kasama ang isang index. Ang index ay maaaring positibo o negatibo.

Halimbawa:

ldr x0, [pc, #24]

Ang ibig sabihin nito ay ang load register X0 na may salitang itinuturo ng nilalaman ng PC plus 24.

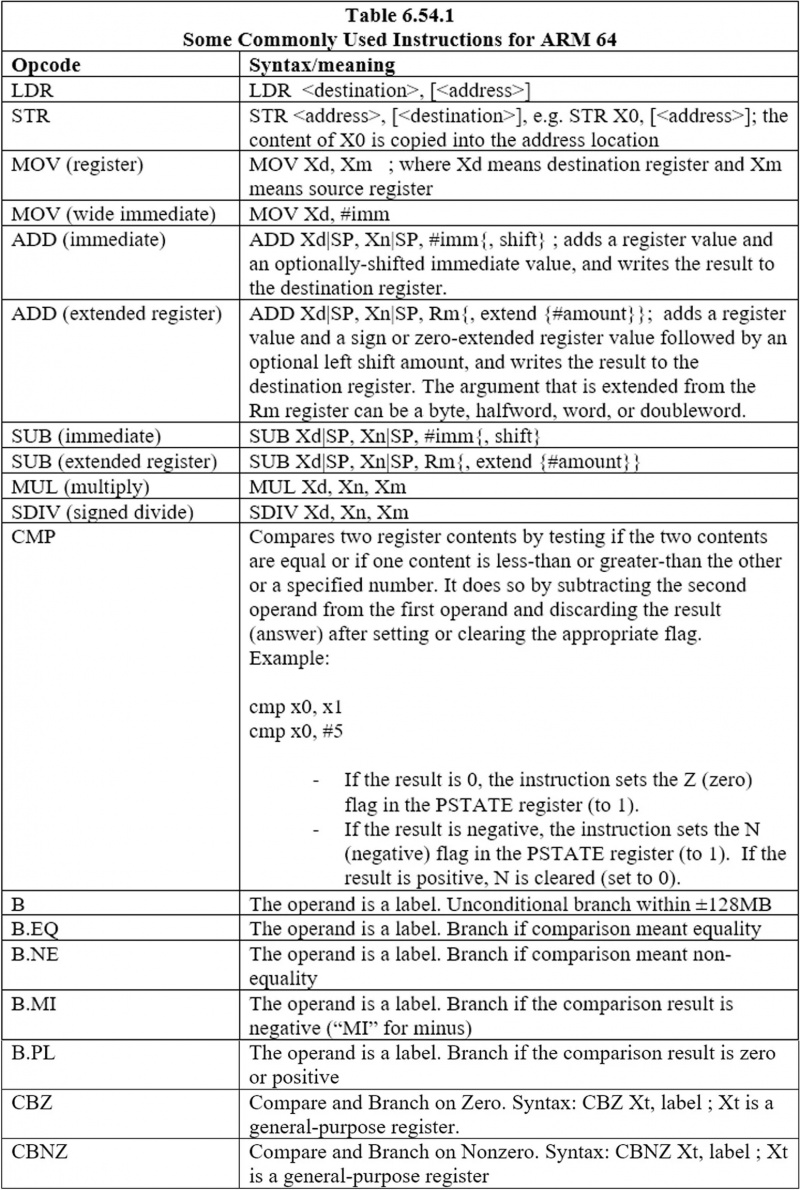

6.44 Ilang Karaniwang Ginagamit na Tagubilin para sa ARM 64

Narito ang mga karaniwang ginagamit na tagubilin:

6.45 Pag-looping

Ilustrasyon

Ang sumusunod na code ay patuloy na nagdaragdag ng value sa X10 register sa value sa X9 hanggang sa zero ang value sa X8. Ipagpalagay na ang lahat ng mga halaga ay mga integer. Ang halaga sa X8 ay binabawasan ng 1 sa bawat pag-ulit:

loop:

CBZ X8, laktawan

ADD X9, X9, X10 ; ang unang X9 ay ang destinasyon at ang pangalawang X9 ay ang pinagmulan

SUB X8, X8, #1 ; ang unang X8 ay ang destinasyon at ang pangalawang X8 ay ang pinagmulan

B loop

laktawan:

Tulad ng 6502 µP at ang X64 µP, ang label sa ARM 64 µP ay magsisimula sa simula ng linya. Ang natitirang mga tagubilin ay nagsisimula sa ilang mga puwang pagkatapos ng simula ng linya. Sa x64 at ARM 64, ang label ay sinusundan ng isang colon at isang bagong linya. Habang may 6502, ang label ay sinusundan ng isang pagtuturo pagkatapos ng isang puwang. Sa nakaraang code, ang unang tagubilin na 'CBZ X8, laktawan' ay nangangahulugan na kung ang halaga sa X8 ay zero, magpatuloy sa label na 'laktawan:', laktawan ang mga tagubilin sa pagitan at magpatuloy sa iba pang mga tagubilin sa ibaba “laktawan:”. Ang 'B loop' ay isang walang kundisyong pagtalon sa label na 'loop'. Anumang ibang pangalan ng label ay maaaring gamitin bilang kapalit ng 'loop'.

Kaya, tulad ng 6502 µP, gamitin ang mga tagubilin sa sangay upang magkaroon ng loop gamit ang ARM 64.

6.46 ARM 64 Input/Output

Ang lahat ng ARM peripheral (mga panloob na port) ay memory na naka-map. Nangangahulugan ito na ang interface ng programming ay isang set ng memory addressed registers (internal ports). Ang address ng naturang rehistro ay isang offset mula sa isang tiyak na address ng base ng memorya. Ito ay katulad ng kung paano ginagawa ng 6502 ang input/output. Ang ARM ay walang opsyon para sa hiwalay na I/O address space.

6.47 Stack ng ARM 64

Ang ARM 64 ay may stack in memory (RAM) sa katulad na paraan na mayroon ang 6502 at x64. Gayunpaman, sa ARM64, walang push o pop opcode. Ang stack sa ARM 64 ay lumalaki din pababa. Ang address sa stack pointer ay tumuturo pagkatapos lamang ng huling byte ng huling halaga na inilagay sa stack.

Ang dahilan kung bakit walang generic na pop o push opcode para sa ARM64 ay pinamamahalaan ng ARM 64 ang stack nito sa mga pangkat ng magkakasunod na 16 byte. Gayunpaman, ang mga halaga ay umiiral sa mga pangkat ng byte ng isang byte, dalawang byte, apat na byte, at 8 byte. Kaya, ang isang halaga ay maaaring ilagay sa stack, at ang iba pang mga lugar (mga lokasyon ng byte) na bubuo para sa 16 na byte ay nilagyan ng mga dummy byte. Ito ay may kawalan ng pag-aaksaya ng memorya. Ang isang mas mahusay na solusyon ay upang punan ang 16-byte na lokasyon ng mas maliliit na halaga at magkaroon ng ilang programmer na nakasulat na code na sumusubaybay kung saan nagmumula ang mga halaga sa 16-byte na lokasyon (nagpaparehistro). Ang dagdag na code na ito ay kailangan din sa pagbawi ng mga halaga. Ang isang alternatibo dito ay upang punan ang dalawang 8-byte na pangkalahatang layunin na rehistro ng magkaibang mga halaga, at pagkatapos ay ipadala ang mga nilalaman ng dalawang 8-byte na rehistro sa isang stack. Kailangan pa rin dito ng dagdag na code para masubaybayan ang mga partikular na maliliit na value na pumapasok sa stack at umalis sa stack.

Ang sumusunod na code ay nag-iimbak ng apat na 4-byte na data sa stack:

str w0, [sp, #-4]!

str w1, [sp, #-8]!

str w2, [sp, #-12]!

str w3, [sp, #-16]!

Ang unang apat na byte (w) ng mga register – x0, x1, x2, at x3 – ay ipinapadala sa 16 na magkakasunod na byte na lokasyon sa stack. Tandaan ang paggamit ng 'str' at hindi 'push'. Pansinin ang tandang padamdam sa dulo ng bawat panuto. Dahil ang memory stack ay lumalaki pababa, ang unang apat na byte na halaga ay magsisimula sa isang posisyon na minus-apat na byte sa ibaba ng nakaraang stack pointer na posisyon. Ang natitirang mga halaga ng apat na byte ay sumusunod, bumababa. Gagawin ng sumusunod na segment ng code ang tama (at sa pagkakasunud-sunod) na katumbas ng pag-pop sa apat na byte:

ldr w3, [sp], #0

ldr w2, [sp], #4

ldr w1, [sp], #8

ldr w0, [sp], #12

Tandaan ang paggamit ng ldr opcode sa halip na pop. Tandaan din na hindi ginagamit dito ang simbolong padamdam.

Ang lahat ng byte sa X0 (8 bytes) at X1 (8 bytes) ay maaaring ipadala sa 16 byte-location sa stack tulad ng sumusunod:

stp x0, x1, [sp, #-16]! ; 8 + 8 = 16

Sa kasong ito, ang mga rehistro ng x2 (w2) at x3 (w3) ay hindi kailangan. Ang lahat ng nais na byte ay nasa X0 at X2 na mga rehistro. Tandaan ang stp opcode para sa pag-iimbak ng mga pares ng mga nilalaman ng rehistro sa RAM. Tandaan din ang simbolong padamdam. Ang katumbas ng pop ay:

ldp x0, x1, [sp], #0

Walang tandang padamdam para sa pagtuturo na ito. Tandaan ang opcode LDP sa halip na LDR para sa paglo-load ng dalawang magkasunod na lokasyon ng data mula sa memory sa dalawang µP register. Tandaan din na ang pagkopya mula sa memorya patungo sa isang µP na rehistro ay naglo-load, hindi dapat ipagkamali sa paglo-load ng isang file mula sa disk patungo sa RAM, at ang pagkopya mula sa isang µP na rehistro sa RAM ay nag-iimbak.

6.48 Subroutine

Ang subroutine ay isang bloke ng code na nagsasagawa ng isang gawain, opsyonal na nakabatay sa ilang argumento at opsyonal na nagbabalik ng resulta. Sa pamamagitan ng convention, ang R0 hanggang R3 na rehistro (apat na rehistro) ay ginagamit upang ipasa ang mga argumento (parameter) sa isang subroutine, at R0 ay ginagamit upang ipasa ang isang resulta pabalik sa tumatawag. Ang isang subroutine na nangangailangan ng higit sa 4 na input ay gumagamit ng stack para sa mga karagdagang input. Para tumawag ng subroutine, gamitin ang link o ang conditional branch na pagtuturo. Ang syntax para sa pagtuturo ng link ay:

BL label

Kung saan ang BL ay ang opcode at ang label ay kumakatawan sa simula (address) ng subroutine. Ang sangay na ito ay walang kondisyon, pasulong o paatras sa loob ng 128MB. Ang syntax para sa conditional branch na pagtuturo ay:

B.cond label

Kung saan ang cond ay ang kundisyon, hal., eq (equal) o ne (not equal). Ang sumusunod na programa ay may doadd subroutine na nagdaragdag ng mga halaga ng dalawang argumento at nagbabalik ng resulta sa R0:

AREA subrout, CODE, READONLY ; Pangalanan ang bloke ng code na ito

ENTRY ; Markahan ang unang tagubilin upang maisagawa

simulan ang MOV r0, #10 ; I-set up ang mga parameter

MOV r1, #3

BL doadd ; Tumawag sa subroutine

ihinto ang MOV r0, #0x18 ; angel_SWreason_ReportException

LDR r1, =0x20026 ; ADP_Stopped_ApplicationExit

SVC #0x123456 ; ARM semihosting (dating SWI)

doadd ADD r0, r0, r1 ; Subroutine code

BX lr ; Bumalik mula sa subroutine

;

WAKAS ; Markahan ang dulo ng file

Ang mga numerong idaragdag ay decimal 10 at decimal 3. Ang unang dalawang linya sa block na ito ng code (program) ay ipapaliwanag sa ibang pagkakataon. Ang susunod na tatlong linya ay nagpapadala ng 10 sa R0 na rehistro at 3 sa R1 na rehistro, at tinatawag din ang doadd subroutine. Ang 'doadd' ay ang label na nagtataglay ng address ng simula ng subroutine.

Ang subroutine ay binubuo lamang ng dalawang linya. Ang unang linya ay nagdaragdag ng nilalaman 3 ng R sa nilalaman 10 ng R0 na nagbibigay-daan sa resulta ng 13 sa R0. Ang pangalawang linya na may BX opcode at LR operand ay bumabalik mula sa subroutine patungo sa caller code.

TAMA

Ang RET opcode sa ARM 64 ay nakikitungo pa rin sa subroutine, ngunit naiiba ang pagpapatakbo sa RTS sa 6502 o RET sa x64, o ang kumbinasyong 'BX LR' sa ARM 64. Sa ARM 64, ang syntax para sa RET ay:

TUWIRANG {Xn}

Ang pagtuturo na ito ay nagbibigay ng pagkakataon para sa programa na magpatuloy sa isang subroutine na hindi subroutine ng tumatawag, o magpatuloy lamang sa ilang iba pang pagtuturo at ang sumusunod na segment ng code. Ang Xn ay isang pangkalahatang layunin na rehistro na nagtataglay ng address kung saan dapat magpatuloy ang programa. Ang pagtuturo na ito ay sumasanga nang walang kondisyon. Nagde-default ito sa nilalaman ng X30 kung hindi ibinigay ang Xn.

Pamantayan ng Pamamaraan sa Pagtawag

Kung gusto ng programmer na makipag-ugnayan ang kanyang code sa isang code na isinulat ng ibang tao o sa isang code na ginawa ng isang compiler, kailangang sumang-ayon ang programmer sa tao o sa manunulat ng compiler sa mga patakaran para sa paggamit ng rehistro. Para sa arkitektura ng ARM, ang mga panuntunang ito ay tinatawag na Pamantayan sa Pagtawag ng Pamamaraan o PCS. Ito ay mga kasunduan sa pagitan ng dalawa o tatlong partido. Tinukoy ng PCS ang mga sumusunod:

- Aling mga rehistro ng µP ang ginagamit upang ipasa ang mga argumento sa function (subroutine)

- Aling mga rehistro ng µP ang ginagamit upang ibalik ang resulta sa function na gumagawa ng pagtawag na kilala bilang ang tumatawag

- Aling µP ang nagrerehistro ng function na tinatawag, na kilala bilang callee, ay maaaring masira

- Aling µP ang nagrerehistro ang tumatawag ay hindi maaaring masira

6.49 Mga interrupt

Mayroong dalawang uri ng interrupt controller circuit na magagamit para sa ARM processor:

- Standard Interrupt Controller: Tinutukoy ng interrupt handler kung aling device ang nangangailangan ng servicing sa pamamagitan ng pagbabasa ng bitmap register ng device sa interrupt controller.

- Vector Interrupt Controller (VIC): Binibigyang-priyoridad ang mga interrupt at pinapasimple ang pagtukoy kung aling device ang naging sanhi ng interrupt. Pagkatapos iugnay ang priyoridad at address ng handler sa bawat interrupt, iginigiit lang ng VIC ang interrupt na signal sa processor kung ang priyoridad ng bagong interrupt ay mas mataas kaysa sa kasalukuyang nagpapagana ng interrupt handler.

Tandaan : Ang pagbubukod ay tumutukoy sa error. Ang mga detalye para sa vector interrupt controller para sa 32-bit ARM computer ay ang mga sumusunod (64 bit ay magkatulad):

| Talahanayan 6.49.1 ARM Vector Exception/Interrupt para sa 32-Bit na Computer |

|||

|---|---|---|---|

| Exception/Interrupt | Maikling Kamay | Address | Mataas na Address |

| I-reset | I-RESET | 0x00000000 | 0xffff0000 |

| Hindi natukoy na pagtuturo | UNDEF | 0x00000004 | 0xffff0004 |

| Pagkagambala ng Software | SWI | 0x00000008 | 0xffff0008 |

| Prefetch abort | pabt | 0x0000000C | 0xffff000C |

| Petsa ng pagpapalaglag | DABT | 0x00000010 | 0xffff0010 |

| Nakareserba | – | 0x00000014 | 0xffff0014 |

| Humiling ng Interrupt | IRQ | 0x00000018 | 0xffff0018 |

| Mabilis na Pag-abala na Kahilingan | FIQ | 0x0000001C | 0xffff001C |

Ito ay kamukha ng arrangement para sa 6502 architecture kung saan NMI , BR , at IRQ maaaring magkaroon ng mga pointer sa page zero, at ang kaukulang mga gawain ay mataas sa memorya (ROM OS). Ang mga maikling paglalarawan ng mga hilera ng nakaraang talahanayan ay ang mga sumusunod:

I-RESET

Nangyayari ito kapag nag-power up ang processor. Sinisimulan nito ang system at ise-set up ang mga stack para sa iba't ibang mga mode ng processor. Ito ang pinakamataas na priyoridad na pagbubukod. Sa pagpasok sa reset handler, ang CPSR ay nasa SVC mode at parehong IRQ at FIQ bits ay nakatakda sa 1, na tinatakpan ang anumang mga abala.

PETSA NG Aborsyon

Ang pangalawang pinakamataas na priyoridad. Nangyayari ito kapag sinubukan naming magbasa/magsulat sa isang di-wastong address o ma-access ang maling pahintulot sa pag-access. Sa pagpasok sa Data Abort Handler, ang mga IRQ ay idi-disable (I-bit set 1) at ang FIQ ay paganahin. Ang mga IRQ ay nakamaskara, ngunit ang mga FIQ ay pinananatiling walang maskara.

FIQ

Ang pinakamataas na priyoridad na interrupt, IRQ at FIQs, ay hindi pinagana hanggang ang FIQ ay mahawakan.

IRQ

Ang mataas na priyoridad na interrupt, ang IRQ handler, ay ipinapasok lamang kung walang on-going FIQ at data abort.

Pre-Fetch Abort

Ito ay katulad ng data abort ngunit nangyayari sa pagkabigo sa pagkuha ng address. Sa pagpasok sa handler, ang mga IRQ ay hindi pinagana ngunit ang mga FIQ ay nananatiling naka-enable at maaaring mangyari sa panahon ng pre-fetch abort.

SWI

Ang isang pagbubukod sa Software Interrupt (SWI) ay nangyayari kapag ang pagtuturo ng SWI ay naisakatuparan at wala sa iba pang mas mataas na priyoridad na mga pagbubukod ang na-flag.

Hindi Natukoy na Pagtuturo

Ang pagbubukod ng Hindi Natukoy na Pagtuturo ay nangyayari kapag ang isang pagtuturo na wala sa set ng pagtuturo ng ARM o Thumb ay umabot sa yugto ng pagpapatupad ng pipeline at wala sa iba pang mga pagbubukod ang na-flag. Ito ay ang parehong priyoridad bilang SWI bilang isa ay maaaring mangyari sa isang pagkakataon. Nangangahulugan ito na ang pagtuturo na isinasagawa ay hindi maaaring maging isang pagtuturo ng SWI at isang hindi natukoy na pagtuturo sa parehong oras.

Paghawak ng ARM Exception

Ang mga sumusunod na kaganapan ay nangyayari kapag ang isang pagbubukod ay nangyari:

- Itabi ang CPSR sa SPSR ng exception mode.

- Ang PC ay nakaimbak sa LR ng exception mode.

- Ang link register ay nakatakda sa isang partikular na address batay sa kasalukuyang pagtuturo. Halimbawa: para sa ISR, LR = huling naisakatuparan na pagtuturo + 8.

- I-update ang CPSR tungkol sa exception.

- Itakda ang PC sa address ng exception handler.

6.5 Mga Tagubilin at Data

Ang data ay tumutukoy sa mga variable (mga label na may kanilang mga halaga) at mga array at iba pang mga istraktura na katulad ng array. Ang string ay parang array ng mga character. Isang hanay ng mga integer ang makikita sa isa sa mga nakaraang kabanata. Ang mga tagubilin ay tumutukoy sa mga opcode at kanilang mga operand. Ang isang programa ay maaaring isulat gamit ang mga opcode at data na pinaghalo sa isang patuloy na seksyon ng memorya. Ang pamamaraang iyon ay may mga kawalan ngunit hindi inirerekomenda.

Ang isang programa ay dapat na nakasulat muna sa mga tagubilin, na sinusundan ng data (pangmaramihan ng datum ay data). Ang paghihiwalay sa pagitan ng mga tagubilin at data ay maaaring ilang byte lang. Para sa isang programa, ang parehong mga tagubilin at ang data ay maaaring nasa isa o dalawang magkahiwalay na seksyon sa memorya.

6.6 Ang Arkitektura ng Harvard

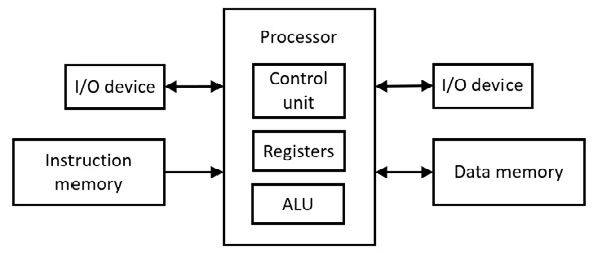

Ang isa sa mga unang computer ay tinatawag na Harvard Mark I (1944). Ang isang mahigpit na arkitektura ng Harvard ay gumagamit ng isang address space para sa mga tagubilin ng programa at isang iba't ibang hiwalay na address space para sa data. Nangangahulugan ito na mayroong dalawang magkahiwalay na alaala. Ang sumusunod ay nagpapakita ng arkitektura:

Larawan 6.71 Arkitektura ng Harvard

Ginagawa ng Control Unit ang pag-decode ng pagtuturo. Ginagawa ng Arithmetic Logic Unit (ALU) ang mga pagpapatakbo ng arithmetic na may combinational logic (gate). Ginagawa rin ng ALU ang mga lohikal na operasyon (hal. paglilipat).

Gamit ang 6502 microprocessor, ang isang pagtuturo ay napupunta sa microprocessor muna (control unit) bago ang datum (singular para sa data) ay pumunta sa µP register bago sila makipag-ugnayan. Nangangailangan ito ng hindi bababa sa dalawang pulso ng orasan at hindi ito sabay-sabay na pag-access sa pagtuturo at datum. Sa kabilang banda, ang arkitektura ng Harvard ay nagbibigay ng sabay-sabay na pag-access sa mga tagubilin at data, na may parehong pagtuturo at datum na pumapasok sa µP nang sabay-sabay (opcode para makontrol ang unit at datum sa µP register), na nagse-save ng kahit isang clock pulse. Ito ay isang anyo ng paralelismo. Ang form na ito ng parallelism ay ginagamit sa cache ng hardware sa mga modernong motherboards (sumangguni sa sumusunod na talakayan).

6.7 Memorya ng Cache

Ang Cache Memory (RAM) ay isang high-speed na rehiyon ng memorya (kumpara sa bilis ng pangunahing memorya) na pansamantalang nag-iimbak ng mga tagubilin ng programa o data para magamit sa hinaharap. Ang cache memory ay tumatakbo nang mas mabilis kaysa sa pangunahing memorya. Karaniwan, ang mga tagubilin o data item na ito ay kinukuha mula sa kamakailang pangunahing memorya at malamang na kailanganin muli sa ilang sandali. Ang pangunahing layunin ng cache memory ay upang taasan ang bilis ng paulit-ulit na pag-access sa parehong mga pangunahing lokasyon ng memorya. Upang maging epektibo, ang pag-access sa mga naka-cache na item ay dapat na mas mabilis kaysa sa pag-access sa orihinal na pinagmulan ng mga tagubilin o data na tinutukoy bilang Backing Store.

Kapag ginagamit ang caching, ang bawat pagtatangka na ma-access ang isang pangunahing lokasyon ng memorya ay magsisimula sa paghahanap ng cache. Kung ang hiniling na item ay naroroon, ang processor ay kukuha at gagamitin ito kaagad. Ito ay tinatawag na Cache Hit. Kung ang paghahanap ng cache ay hindi matagumpay (isang cache miss), ang pagtuturo o data item ay dapat na makuha mula sa backing store (pangunahing memorya). Sa proseso ng pagkuha ng hiniling na item, isang kopya ay idinagdag sa cache para sa isang inaasahang malapit na paggamit sa hinaharap.

Yunit ng Pamamahala ng Memorya

Ang Memory Management Unit (MMU) ay isang circuit na namamahala sa pangunahing memorya at mga nauugnay na memory register sa motherboard. Noong nakaraan, ito ay isang hiwalay na integrated circuit sa motherboard; ngunit ngayon, ito ay karaniwang bahagi ng microprocessor. Dapat ding pamahalaan ng MMU ang cache (circuit) na bahagi rin ng microprocessor ngayon. Ang cache circuit ay isang hiwalay na integrated circuit sa nakaraan.

Static na RAM

Ang Static RAM (SRAM) ay may mas mabilis na oras ng pag-access kaysa sa DRAM, kahit na sa kapinsalaan ng mas kumplikadong circuitry. Ang mga bit cell ng SRAM ay kumukuha ng mas maraming espasyo sa integrated circuit die kaysa sa mga cell ng isang DRAM device na may kakayahang mag-imbak ng katumbas na dami ng data. Ang pangunahing memorya (RAM) ay karaniwang binubuo ng DRAM (Dynamic RAM).